**CONTROLLER MANUAL**

# F<sup>2</sup>MC<sup>TM</sup>-16LX 16-BIT MICROCONTROLLER MB90360 Series HARDWARE MANUAL

# F<sup>2</sup>MC<sup>TM</sup>-16LX 16-BIT MICROCONTROLLER MB90360 Series HARDWARE MANUAL

# **PREFACE**

# ■ Objectives and intended reader

Thank you very much for your continued patronage of Fujitsu semiconductor products.

The MB90360 series has been developed as a general-purpose version of the  $F^2MC-16LX$  family, which is an original 16-bit single-chip microcontroller compatible with the Application Specific IC (ASIC).

This manual explains the functions and operation of the MB90360 series for engineers who actually use the MB90360 series to design products. Please read this manual first.

### ■ Trademark

F<sup>2</sup>MC, an abbreviation of FUJITSU Flexible Microcontroller, is a registered trademark of FUJITSU Ltd

Embedded Algorithm is a registered trademark of Advanced Micro Devices Inc.

# ■ Structure of this preliminary manual

This manual contains the following 26 chapters and appendix.

#### **CHAPTER 1 OVERVIEW**

The MB90360 Series is a family member of the F<sup>2</sup>MC-16LX micro controllers.

# **CHAPTER 2 CPU**

This chapter explains the CPU.

#### **CHAPTER 3 INTERRUPTS**

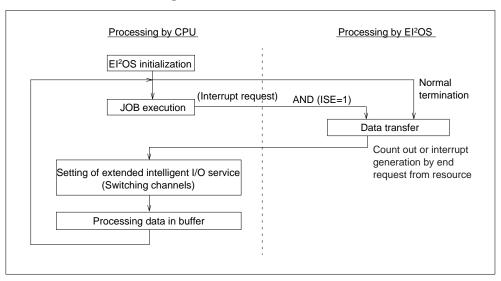

This chapter explains the interrupts and function and operation of the extended intelligent I/O service in the MB90360 series.

# **CHAPTER 4 DELAYED INTERRUPT GENERATION MODULE**

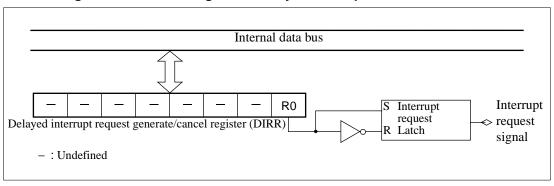

This chapter explains the functions and operations of the delayed interrupt generation module.

# **CHAPTER 5 CLOCKS**

This chapter explains the clocks used by MB90360 series microcontrollers.

#### **CHAPTER 6 CLOCK SUPERVISOR**

This chapter explains the function and the operation of the clock supervisor. Only the product with built-in clock supervisor of the MB90360 series is valid to this function.

# **CHAPTER 7 RESETS**

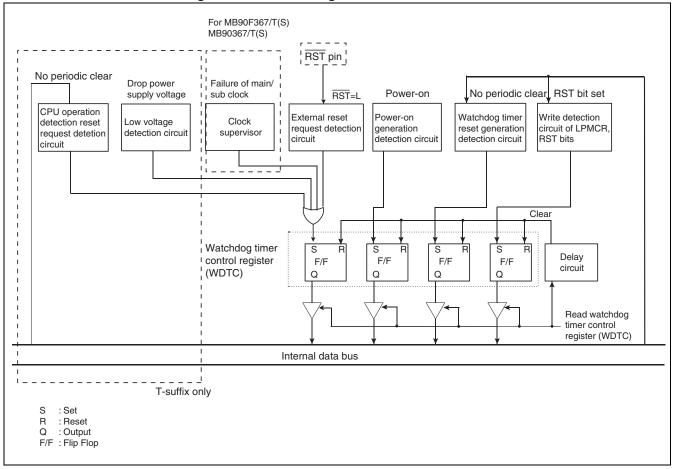

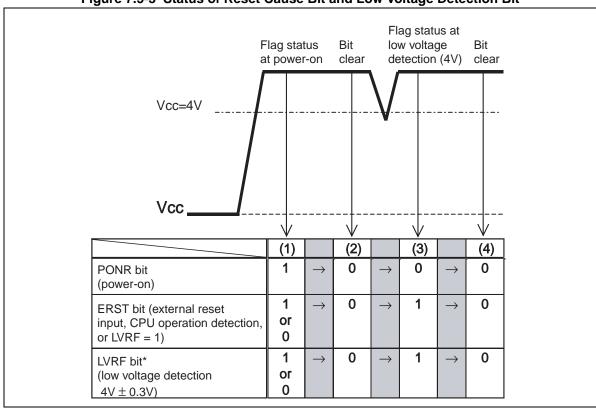

This chapter describes resets for the MB90360-series microcontrollers.

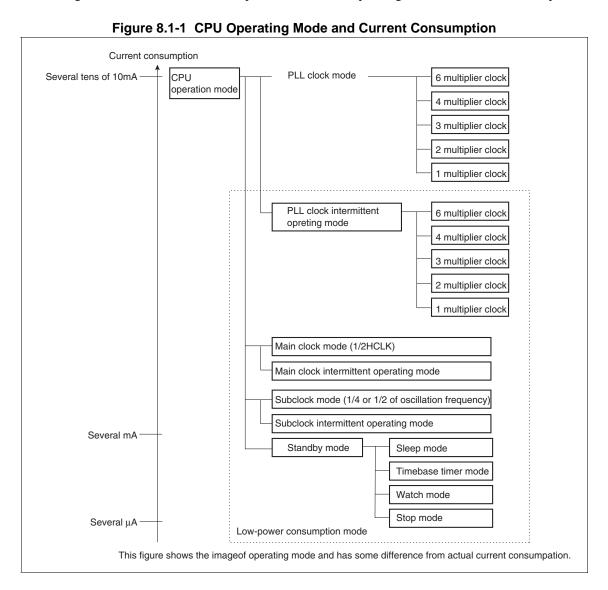

#### **CHAPTER 8 LOW-POWER CONSUMPTION MODE**

This chapter explains the low-power consumption mode of MB90360 series microcontrollers.

#### **CHAPTER 9 MEMORY ACCESS MODES**

This chapter explains the functions and operations of the memory access modes.

#### **CHAPTER 10 I/O PORTS**

This chapter explains the functions and operations of the I/O ports.

#### **CHAPTER 11 TIMEBASE TIMER**

This chapter explains the functions and operations of the timebase timer.

#### **CHAPTER 12 WATCHDOG TIMER**

This chapter describes the function and operation of the watchdog timer.

# CHAPTER 13 16-Bit I/O TIMER

This chapter explains the function and operation of the 16- bit I/O timer.

#### **CHAPTER 14 16-BIT RELOAD TIMER**

This chapter describes the functions and operation of the 16-bit reload timer.

# **CHAPTER 15 WATCH TIMER**

This chapter describes the functions and operations of the watch timer.

#### **CHAPTER 16 8-/16-BIT PPG TIMER**

This chapter describes the functions and operations of the 8-/16-bit PPG timer.

#### **CHAPTER 17 DTP/EXTERNAL INTERRUPTS**

This chapter explains the functions and operations of DTP/external interrupt.

#### **CHAPTER 18 8-/10-BIT A/D CONVERTER**

This chapter explains the functions and operation of 8-/10-bit A/D converter.

### CHAPTER 19 LOW VOLTAGE DETECTION/CPU OPERATING DETECTION RESET

This chapter explains the function and operating the low voltage detection/CPU operating detection reset. This function can use only the product with "T" suffix of MB90360 series.

#### **CHAPTER 20 LIN-UART**

This chapter explains the functions and operation of LIN-UART.

# **CHAPTER 21 CAN CONTROLLER**

This chapter explains the functions and operations of the CAN controller.

# **CHAPTER 22 ADDRESS MATCH DETECTION FUNCTION**

This chapter explains the address match detection function and its operation.

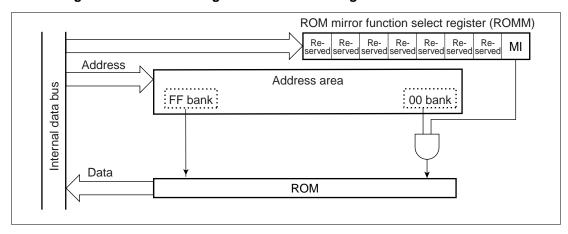

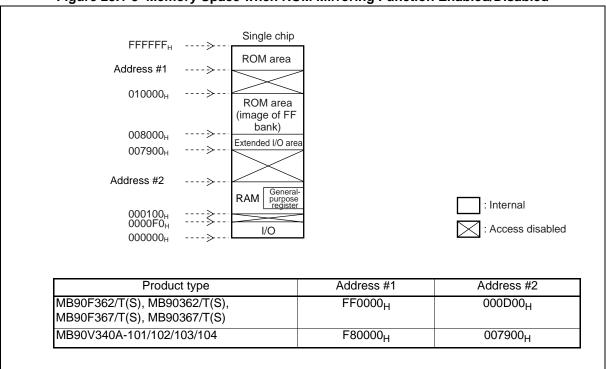

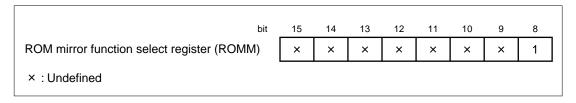

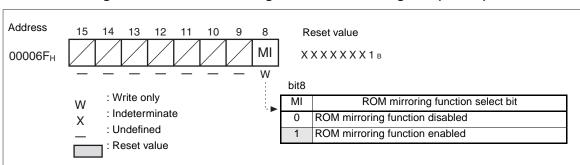

#### **CHAPTER 23 ROM MIRRORING MODULE**

This chapter describes the functions and operations of the ROM mirroring function select module.

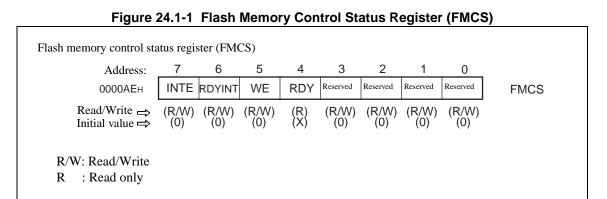

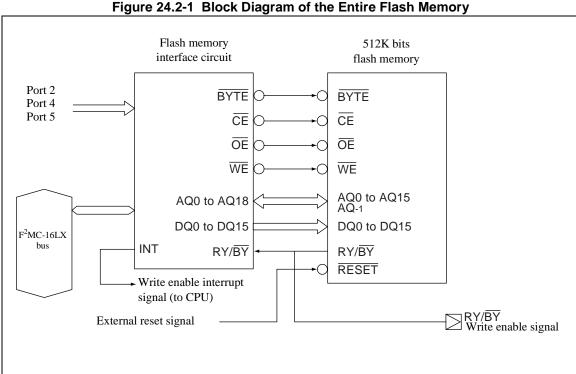

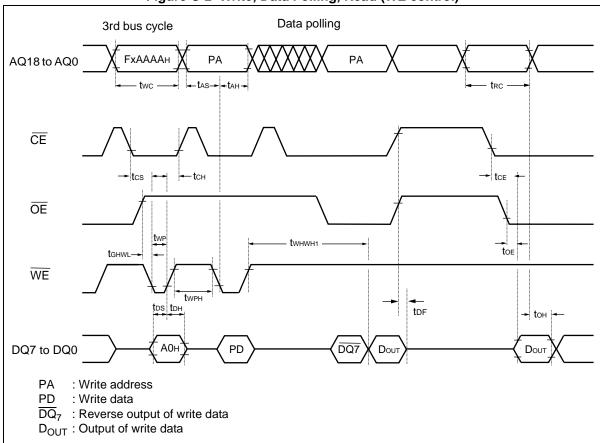

#### **CHAPTER 24 512K-BIT FLASH MEMORY**

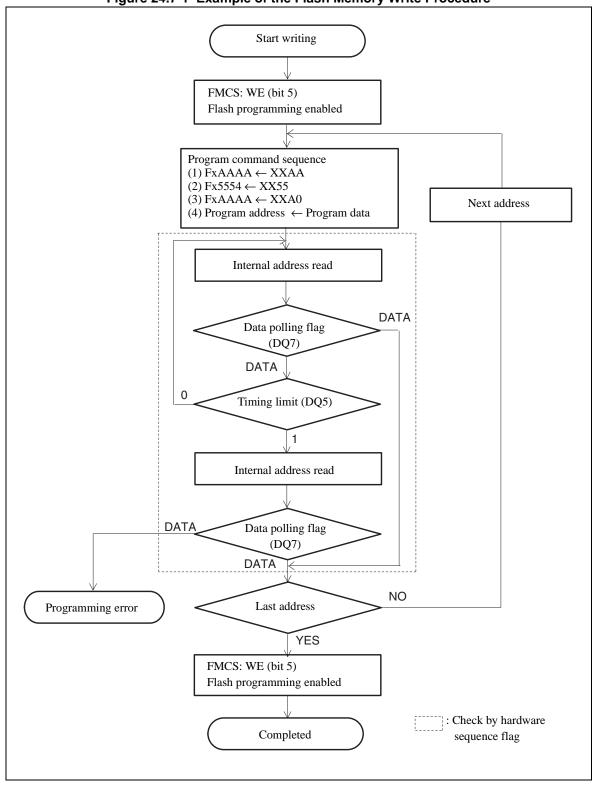

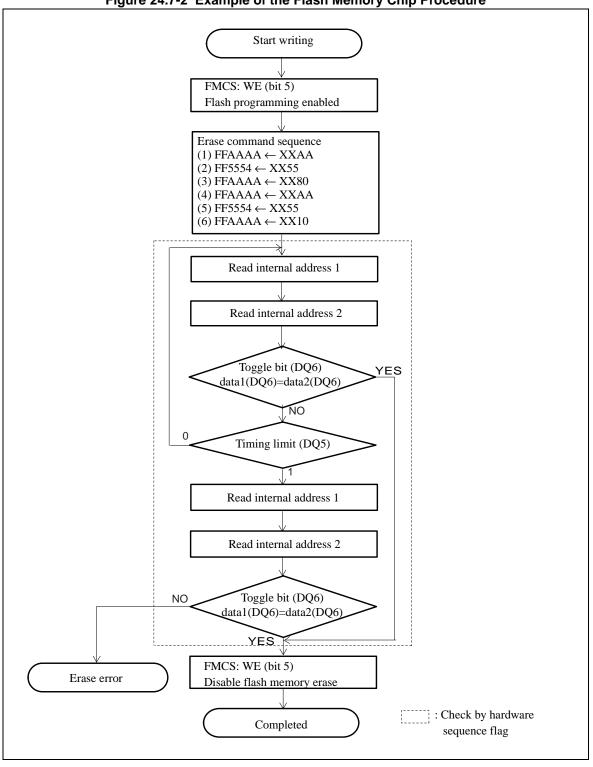

This chapter explains the functions and operation of the 512K-bit flash memory. The following three methods are available for writing data to and erasing data from the flash memory:

- Parallel programmer

- Serial programmer

- Executing programs to write/erase data

This chapter explains "Executing programs to write/erase data".

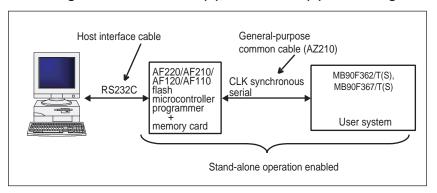

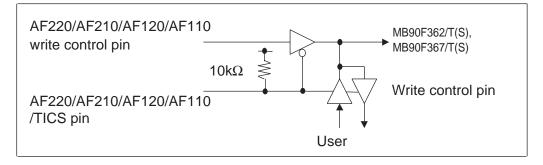

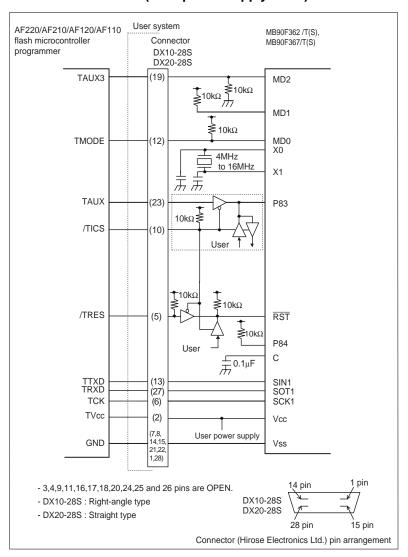

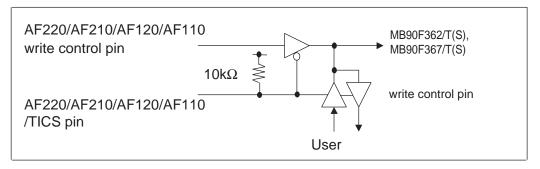

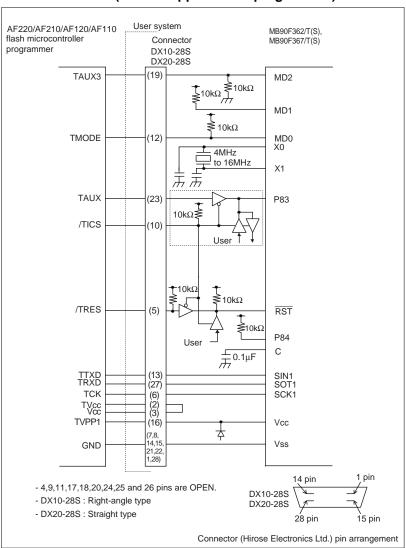

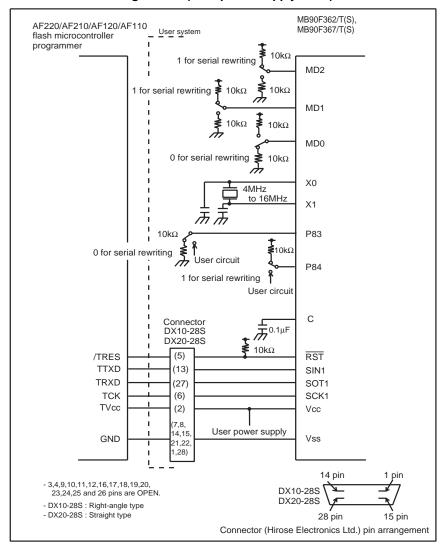

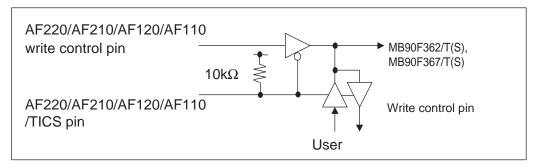

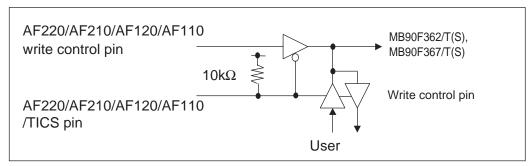

# CHAPTER 25 EXAMPLES OF MB90F362/T(S), MB90F367/T(S) SERIAL PROGRAMMING CONNECTION

This chapter shows an example of a serial programming connection using the AF220/AF210/AF120/AF110 Flash Micro-computer Programmer by Yokogawa Digital Computer Corporation when the AF220/AF210/AF120/AF110 flash serial microcontroller programer from Yokogawa Digital Computer Corporation is used.

# **CHAPTER 26 ROM SECURITY FUNCTION**

This chapter explains the ROM security function.

# **APPENDIX**

The appendixes provide I/O maps, instructions, and other information.

- The contents of this document are subject to change without notice.

Customers are advised to consult with FUJITSU sales representatives before ordering.

- The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.

- Any information in this document, including descriptions of function and schematic diagrams, shall not be

construed as license of the use or exercise of any intellectual property right, such as patent right or

copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any

third-party's intellectual property right or other right by using such information. Fujitsu assumes no

liability for any infringement of the intellectual property rights or other rights of third parties which would

result from the use of information contained herein.

- The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

- Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

- Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage

or loss from such failures by incorporating safety design measures into your facility and equipment such

as redundancy, fire protection, and prevention of over-current levels and other abnormal operating

conditions.

- If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

# **CONTENTS**

| CHAPTE | R 1 OVERVIEW                                                                                        | . 1 |

|--------|-----------------------------------------------------------------------------------------------------|-----|

| 1.1    | Overview of MB90360                                                                                 | 2   |

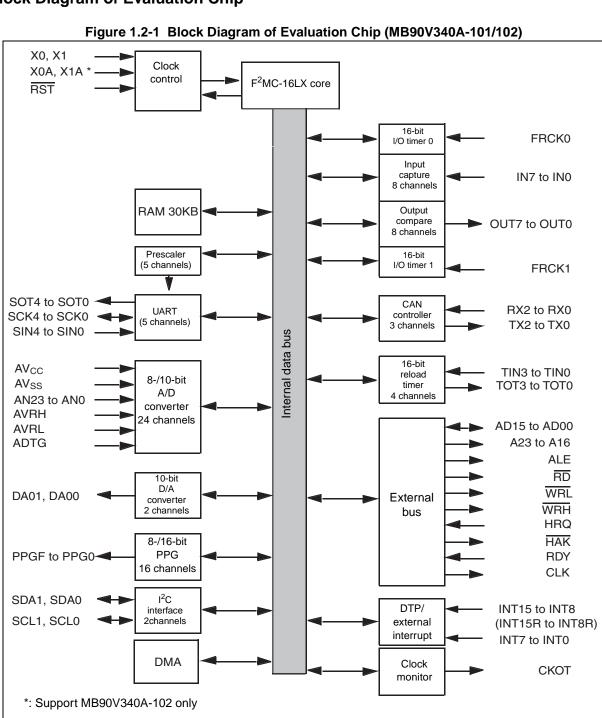

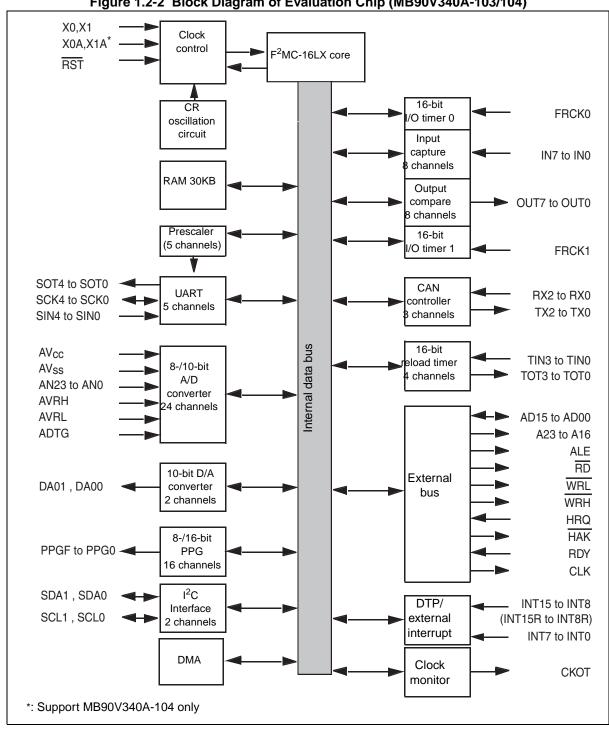

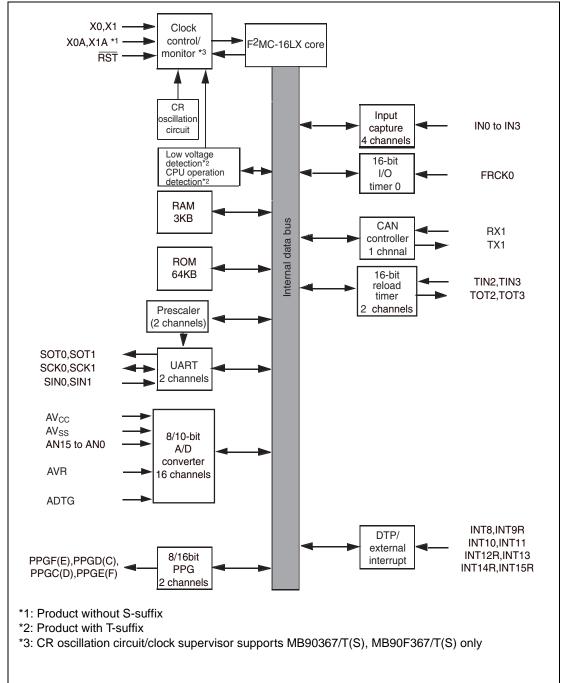

| 1.2    | Block Diagram of MB90360 series                                                                     | 9   |

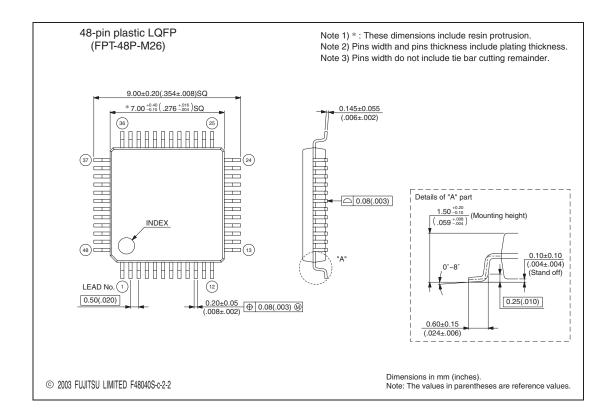

| 1.3    | Package Dimensions                                                                                  | 12  |

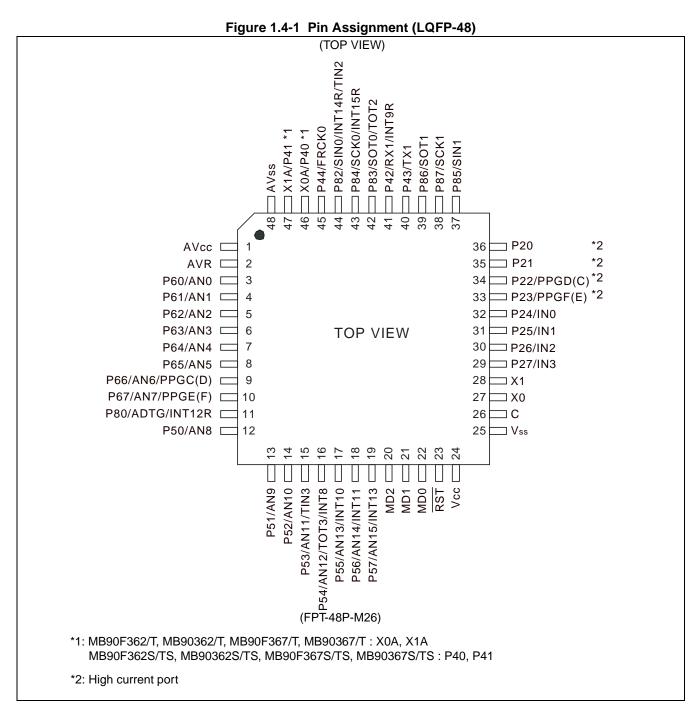

| 1.4    | Pin Assignment                                                                                      | 13  |

| 1.5    | Pin Functions                                                                                       | 14  |

| 1.6    | Input-Output Circuits                                                                               | 17  |

| 1.7    | Handling Device                                                                                     | 21  |

| CHAPTE | ER 2 CPU                                                                                            | 27  |

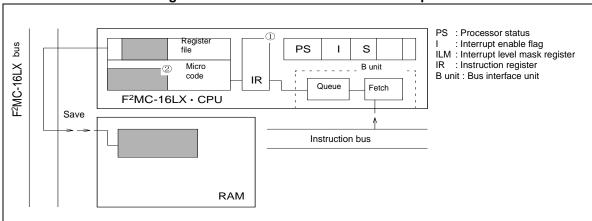

| 2.1    | Outline of the CPU                                                                                  | 28  |

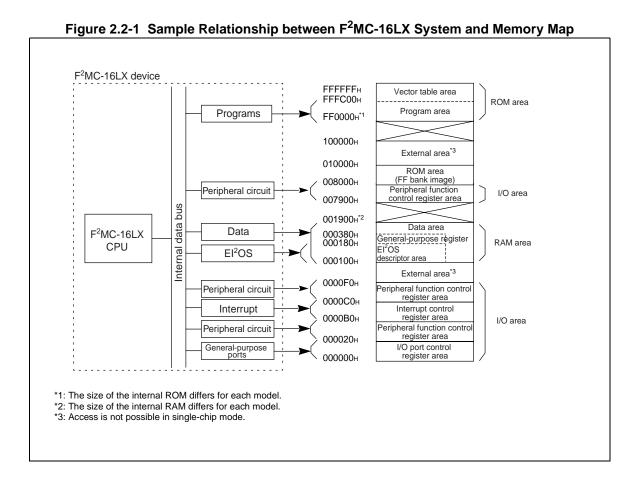

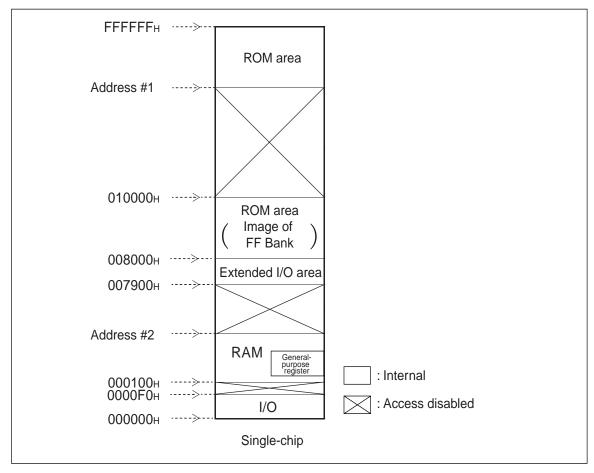

| 2.2    | Memory Space                                                                                        | 29  |

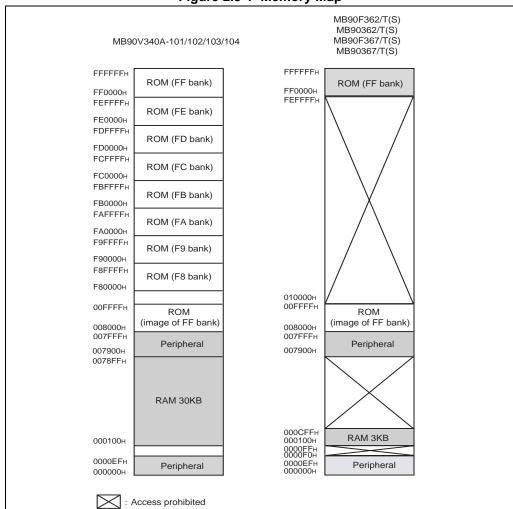

| 2.3    | Memory Map                                                                                          | 32  |

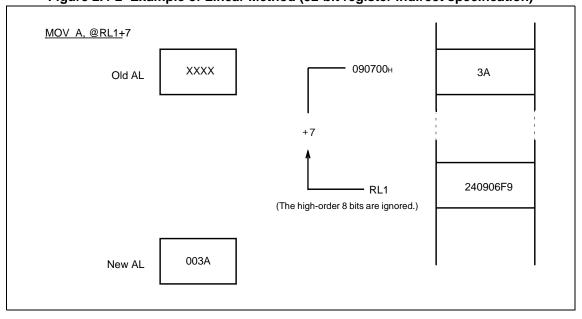

| 2.4    | Linear Addressing                                                                                   | 33  |

| 2.5    | Bank Addressing Types                                                                               | 34  |

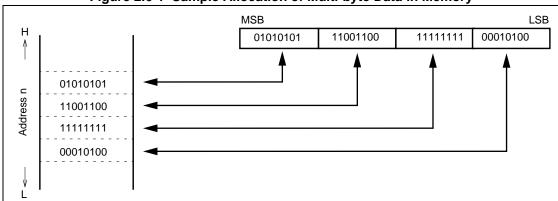

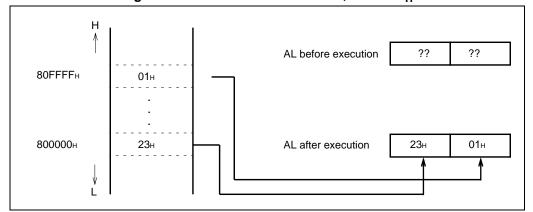

| 2.6    | Multi-byte Data in Memory Space                                                                     | 36  |

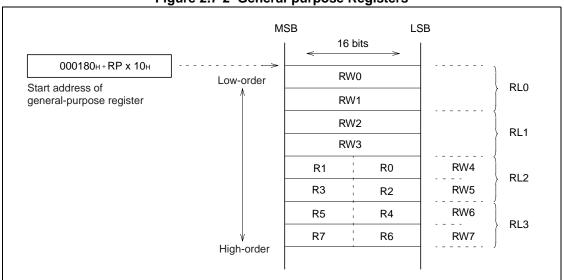

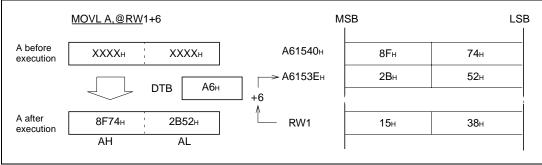

| 2.7    | Registers                                                                                           | 37  |

| 2.7.1  | Accumulator (A)                                                                                     | 40  |

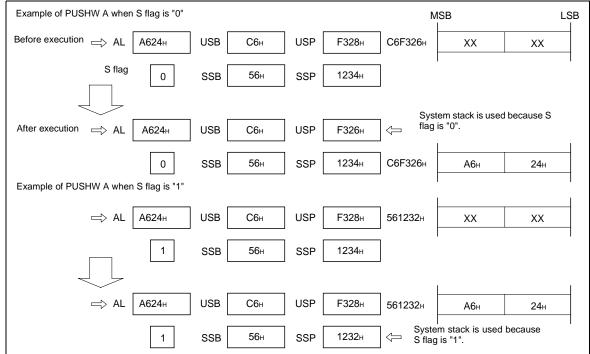

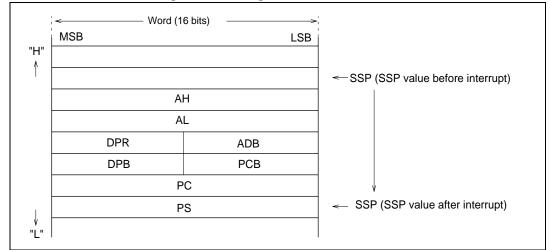

| 2.7.2  | User Stack Pointer (USP) and System Stack Pointer (SSP)                                             | 41  |

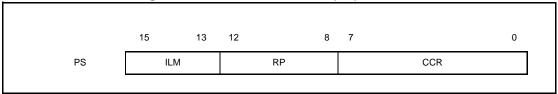

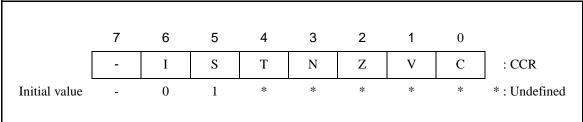

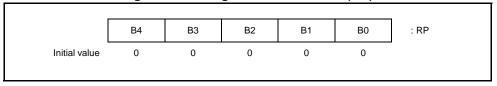

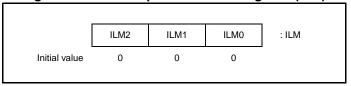

| 2.7.3  | Processor Status (PS)                                                                               | 42  |

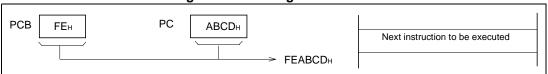

| 2.7.4  | Program Counter (PC)                                                                                | 45  |

| 2.8    | Register Bank                                                                                       | 46  |

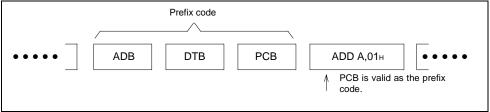

| 2.9    | Prefix Codes                                                                                        | 48  |

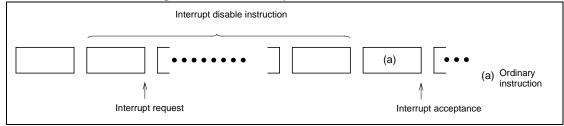

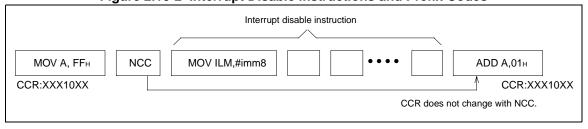

| 2.10   | Interrupt Disable Instructions                                                                      | 51  |

| 2.11   | Precautions for Use of "DIV A, Ri" and "DIVW A, RWi" Instructions                                   | 52  |

| CHAPTE | ER 3 INTERRUPTS                                                                                     | 55  |

| 3.1    | Outline of Interrupts                                                                               | 56  |

| 3.2    | Interrupt Vector                                                                                    | 59  |

| 3.3    | Interrupt Control Registers (ICR)                                                                   | 61  |

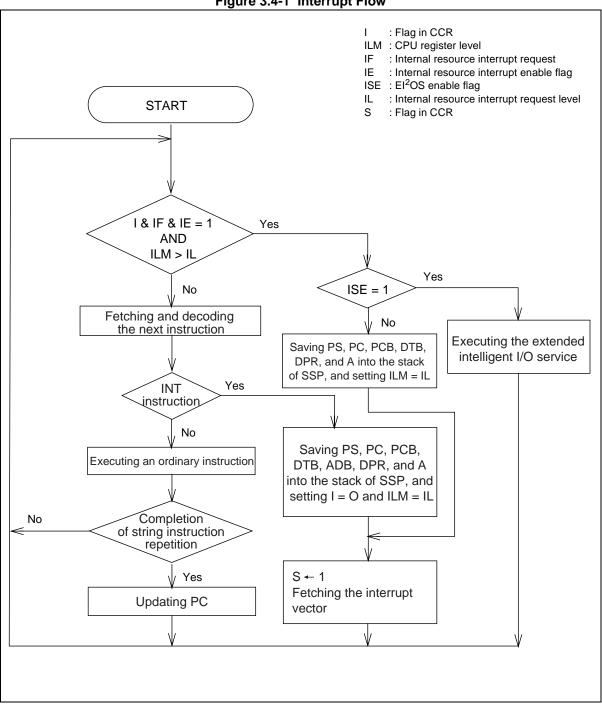

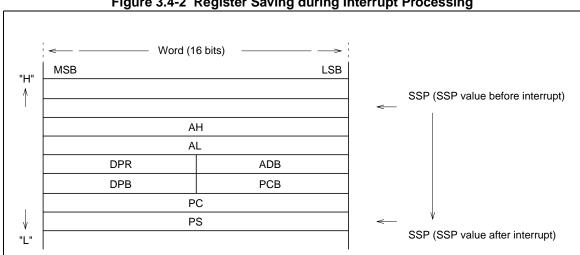

| 3.4    | Interrupt Flow                                                                                      | 65  |

| 3.5    | Hardware Interrupts                                                                                 | 67  |

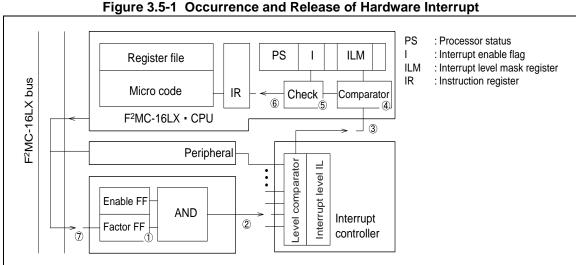

| 3.5.1  | Hardware Interrupt Operation                                                                        | 68  |

| 3.5.2  | Occurrence and Release of Hardware Interrupt                                                        | 69  |

| 3.5.3  | Multiple interrupts                                                                                 | 71  |

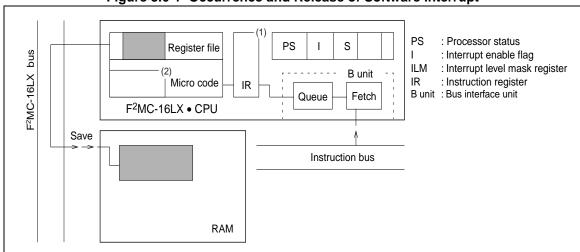

| 3.6    | Software Interrupts                                                                                 | 72  |

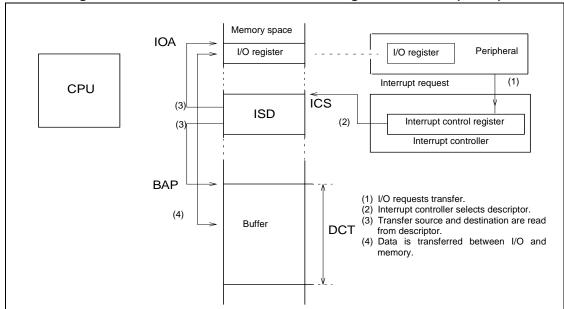

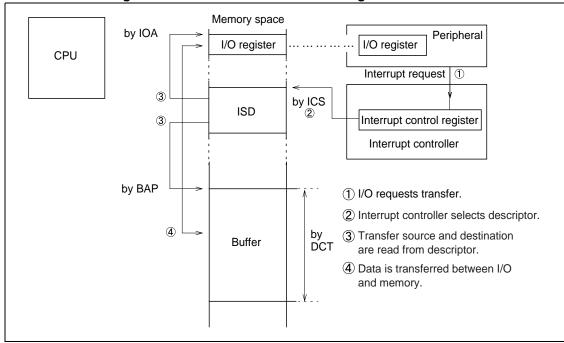

| 3.7    | Extended Intelligent I/O Service (EI <sup>2</sup> OS)                                               | 74  |

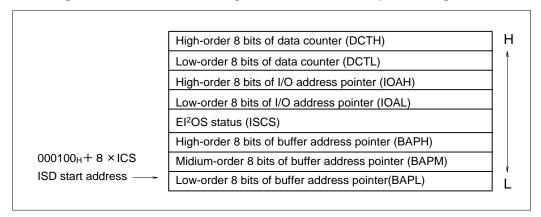

| 3.7.1  | Extended Intelligent I/O Service Descriptor (ISD)                                                   | 76  |

| 3.7.2  | EI <sup>2</sup> OS Status Register (ISCS)                                                           | 78  |

| 3.8    | Operation Flow of and Procedure for Using the Extended Intelligent I/O Service (EI <sup>2</sup> OS) | 79  |

| 3.9    | Exceptions                                                                                          | 82  |

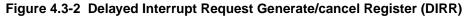

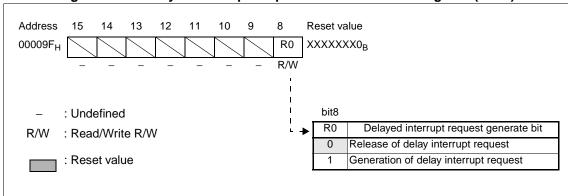

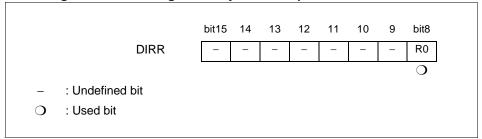

| CHAPT | TER 4 DELAYED INTERRUPT GENERATION MODULE                               | 83  |

|-------|-------------------------------------------------------------------------|-----|

| 4.1   | Overview of Delayed Interrupt Generation Module                         | 84  |

| 4.2   | Block Diagram of Delayed Interrupt Generation Module                    |     |

| 4.3   | Configuration of Delayed Interrupt Generation Module                    |     |

| 4.3.  | · · · · · · · · · · · · · · · · · · ·                                   |     |

| 4.4   | Explanation of Operation of Delayed Interrupt Generation Module         |     |

| 4.5   | Precautions when Using Delayed Interrupt Generation Module              |     |

| 4.6   | Program Example of Delayed Interrupt Generation Module                  |     |

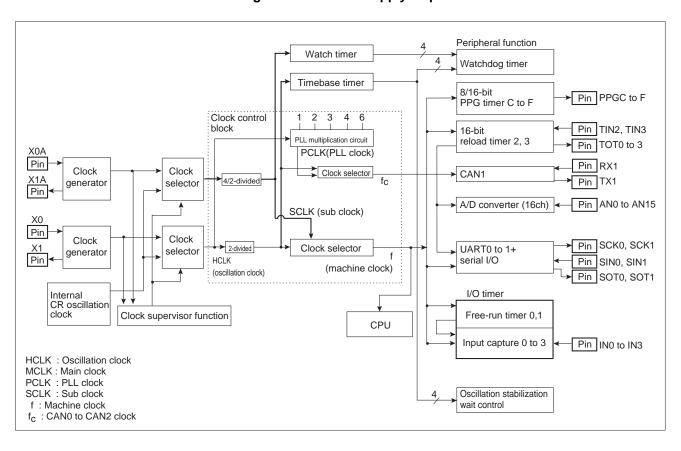

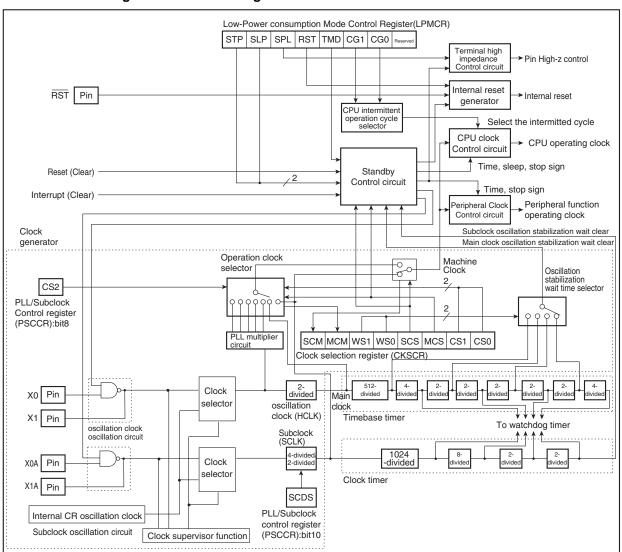

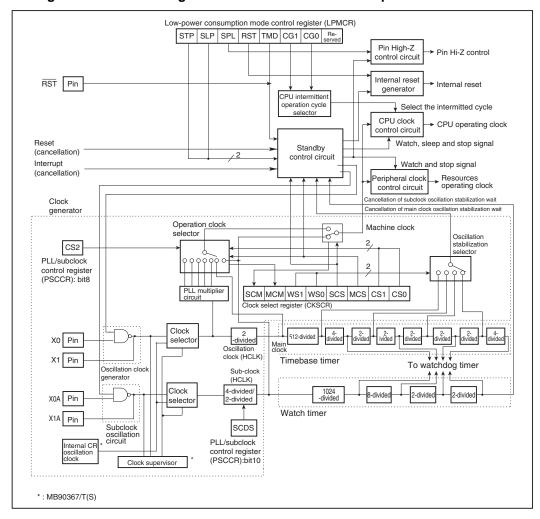

| СНАРТ | TER 5 CLOCKS                                                            | 91  |

| 5.1   | Clocks                                                                  | 92  |

| 5.2   | Block Diagram of the Clock Generation Block                             | 95  |

| 5.2.  | 1 Register of Clock Generation Block                                    | 97  |

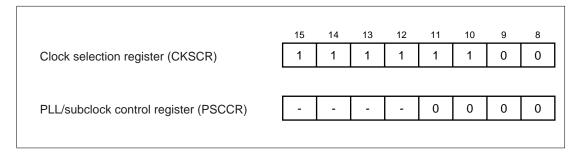

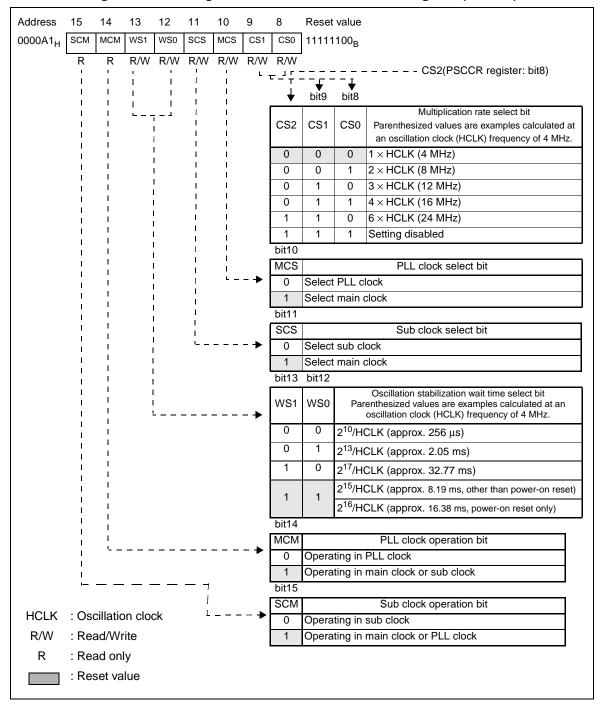

| 5.3   | Clock Selection Register (CKSCR)                                        | 98  |

| 5.4   | PLL/Subclock Control Register (PSCCR)                                   | 101 |

| 5.5   | Clock Mode                                                              | 103 |

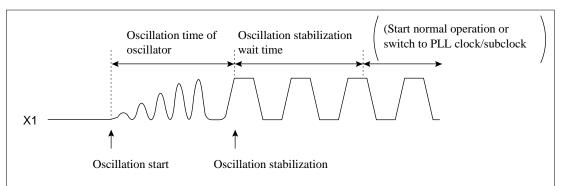

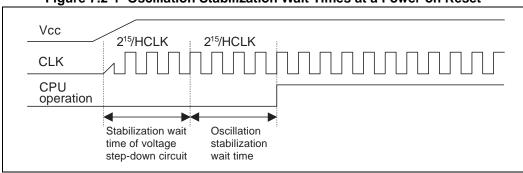

| 5.6   | Oscillation Stabilization Wait Interval                                 | 107 |

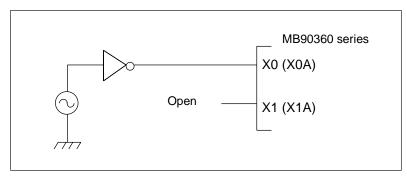

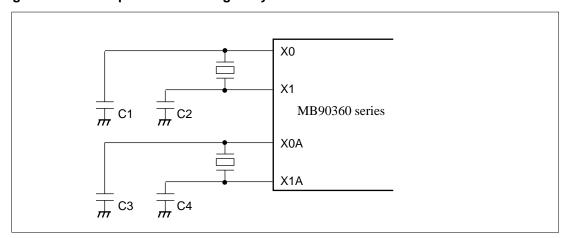

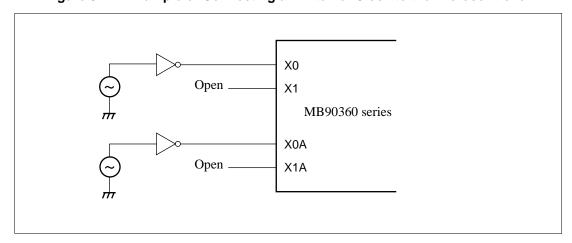

| 5.7   | Connection of an Oscillator or an External Clock to the Microcontroller | 108 |

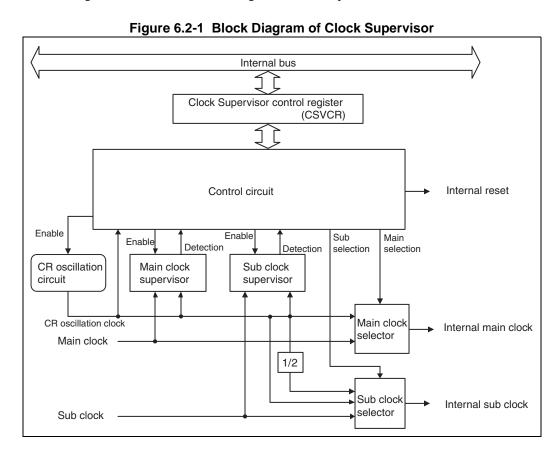

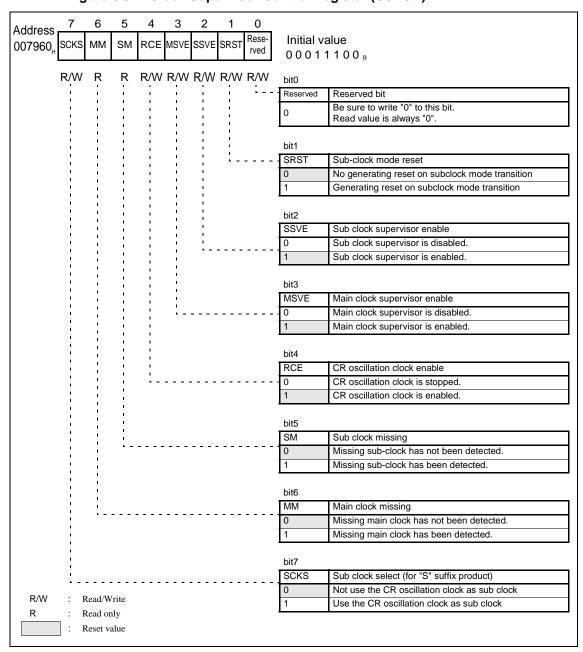

| СНАРТ | TER 6 CLOCK SUPERVISOR                                                  | 109 |

| 6.1   | Overview of Clock Supervisor                                            | 110 |

| 6.2   | Block Diagram of Clock Supervisor                                       | 111 |

| 6.3   | Clock Supervisor Control Register (CSVCR)                               | 113 |

| 6.4   | Operating Mode of Clock Supervisor                                      | 115 |

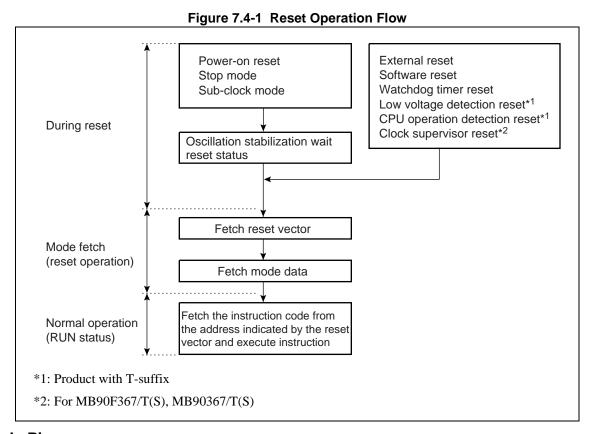

| СНАРТ | TER 7 RESETS                                                            | 119 |

| 7.1   | Resets                                                                  | 120 |

| 7.2   | Reset Cause and Oscillation Stabilization Wait Times                    | 123 |

| 7.3   | External Reset Pin                                                      | 125 |

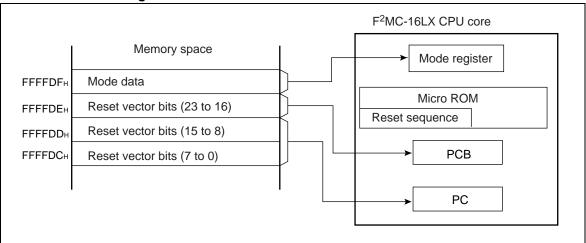

| 7.4   | Reset Operation                                                         | 126 |

| 7.5   | Reset Cause Bits                                                        | 128 |

| 7.6   | Status of Pins in a Reset                                               | 132 |

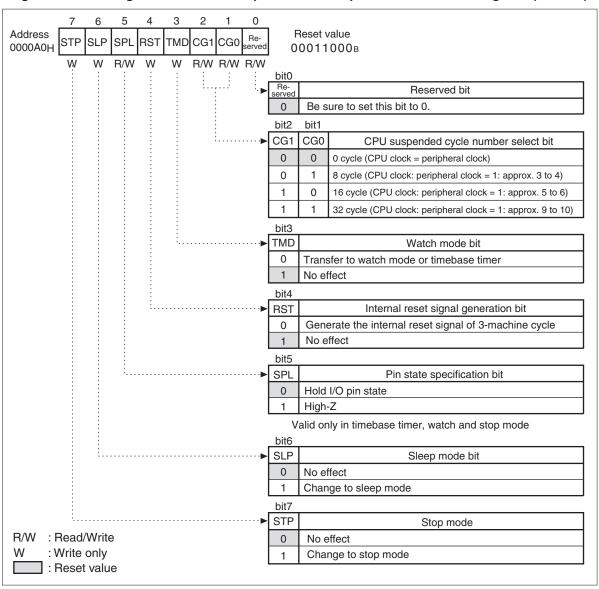

| СНАРТ | TER 8 LOW-POWER CONSUMPTION MODE                                        | 133 |

| 8.1   | Overview of Low-Power Consumption Mode                                  | 134 |

| 8.2   | Block Diagram of the Low-Power Consumption Control Circuit              | 137 |

| 8.3   | Low-Power Consumption Mode Control Register (LPMCR)                     | 139 |

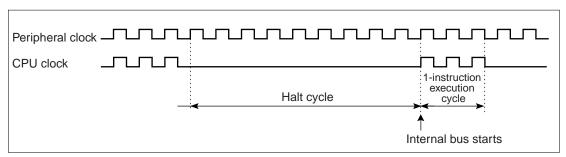

| 8.4   | CPU Intermittent Operation Mode                                         |     |

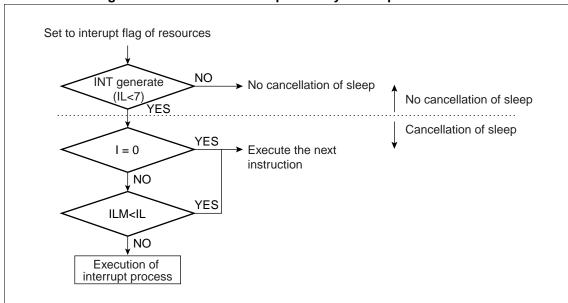

| 8.5   | Standby Mode                                                            | 143 |

| 8.5.  | •                                                                       |     |

| 8.5.  | ·                                                                       |     |

| 8.5.  |                                                                         |     |

| 8.5.  |                                                                         |     |

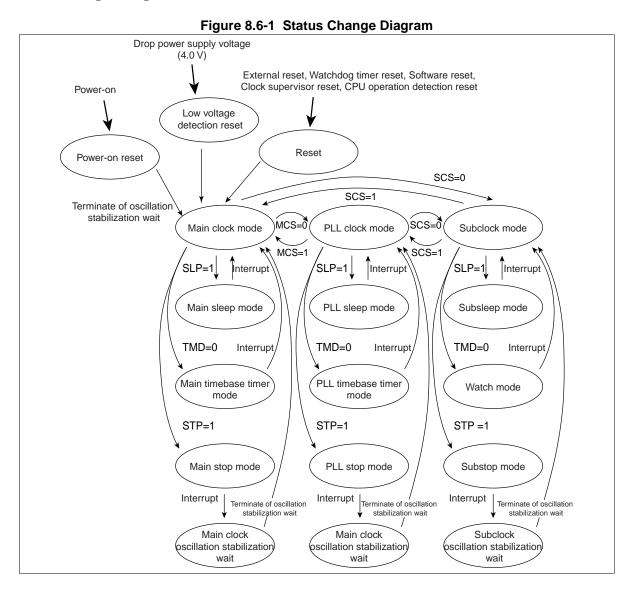

| 8.6   | Status Change Diagram                                                   |     |

| 8.7   | Status of Pins in Standby Mode and during Hold and Reset                |     |

| 8.8   | Usage Notes on Low-Power Consumption Mode                               |     |

| CHAP | TER 9 MEMORY ACCESS MODES                             | 161        |

|------|-------------------------------------------------------|------------|

| 9.1  | Outline of Memory Access Modes                        | 162        |

| 9.1. | 1.1 Mode Pins                                         | 163        |

| 9.1. | 1.2 Mode Data                                         | 164        |

| 9.1. | 1.3 Memory Space in Each Bus Mode                     | 165        |

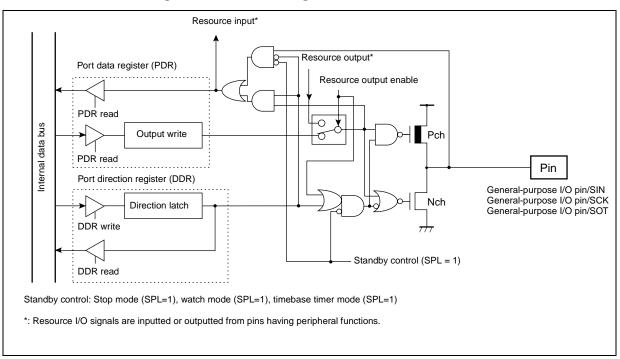

| CHAP | TER 10 I/O PORTS                                      | 167        |

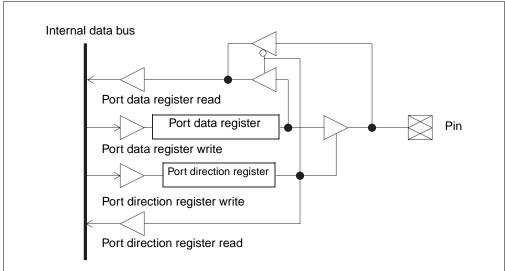

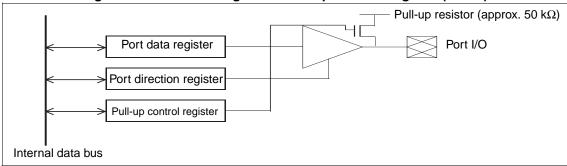

| 10.1 | I/O Ports                                             | 168        |

| 10.2 | l/O Port Registers                                    | 169        |

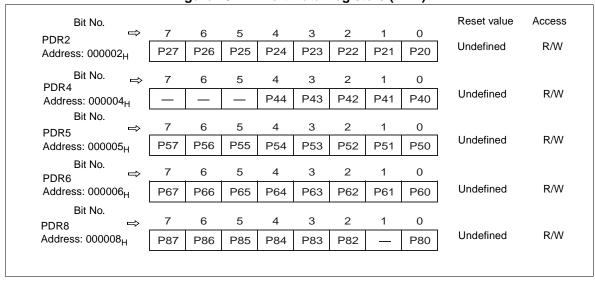

| 10.2 | .2.1 Port Data Register (PDR)                         | 170        |

| 10.2 | .2.2 Port Direction Register (DDR)                    | 172        |

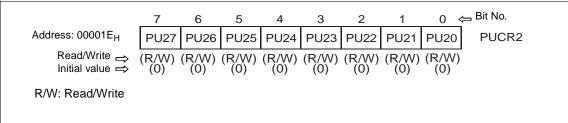

| 10.2 | .2.3 Pull-up Control Register (PUCR)                  | 174        |

| 10.2 | .2.4 Analog Input Enable Register (ADER)              | 175        |

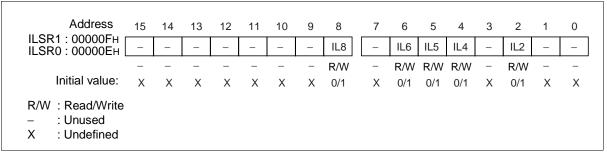

| 10.2 | .2.5 Input Level Select Register                      | 176        |

| CHAP | TER 11 TIMEBASE TIMER                                 | 179        |

| 11.1 | Overview of Timebase Timer                            | 180        |

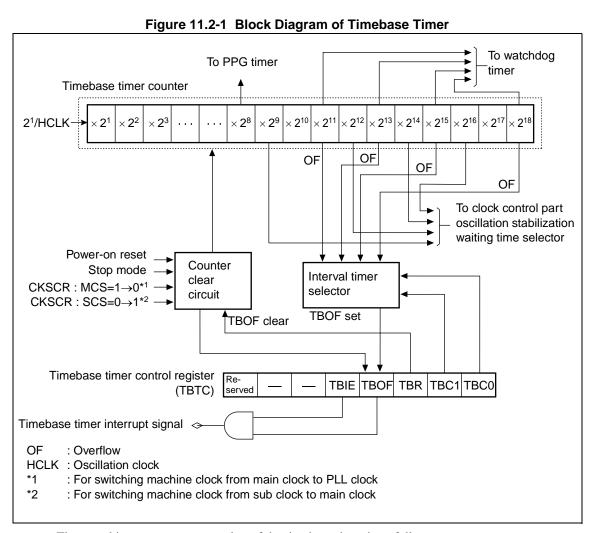

| 11.2 | Block Diagram of Timebase Timer                       | 182        |

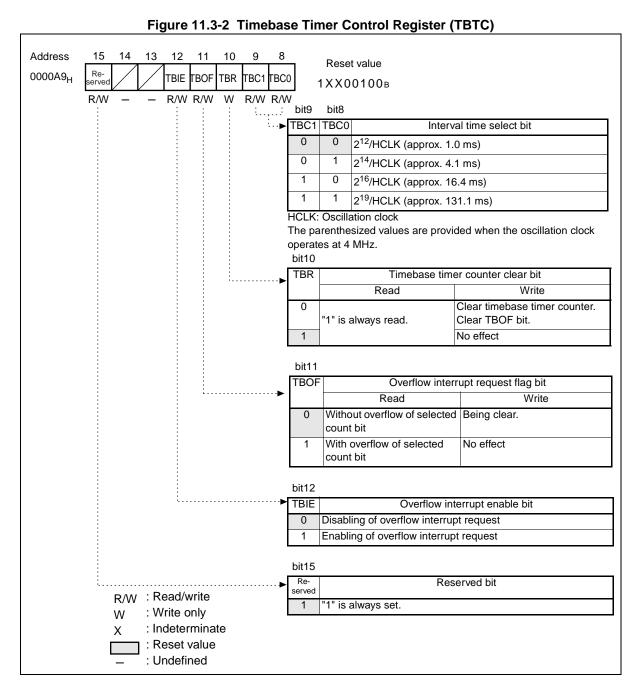

| 11.3 | Configuration of Timebase Timer                       | 184        |

| 11.3 | .3.1 Timebase timer control register (TBTC)           | 185        |

| 11.4 |                                                       |            |

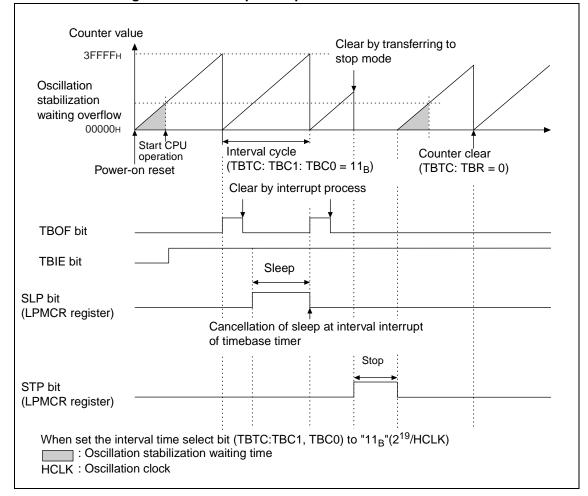

| 11.5 | Explanation of Operations of Timebase Timer Functions | 188        |

| 11.6 | ·                                                     |            |

| 11.7 | _                                                     |            |

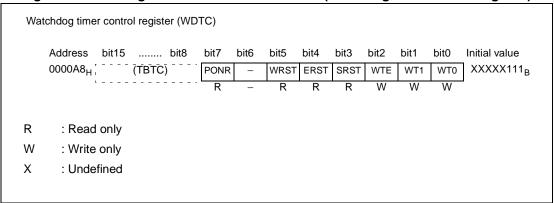

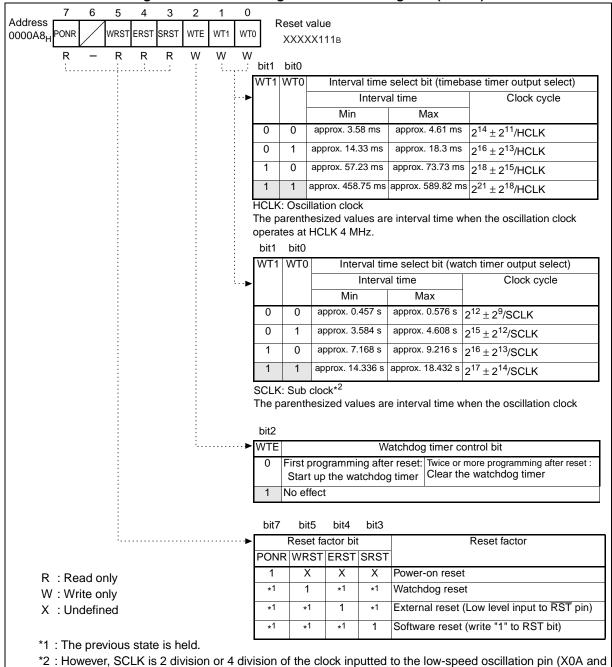

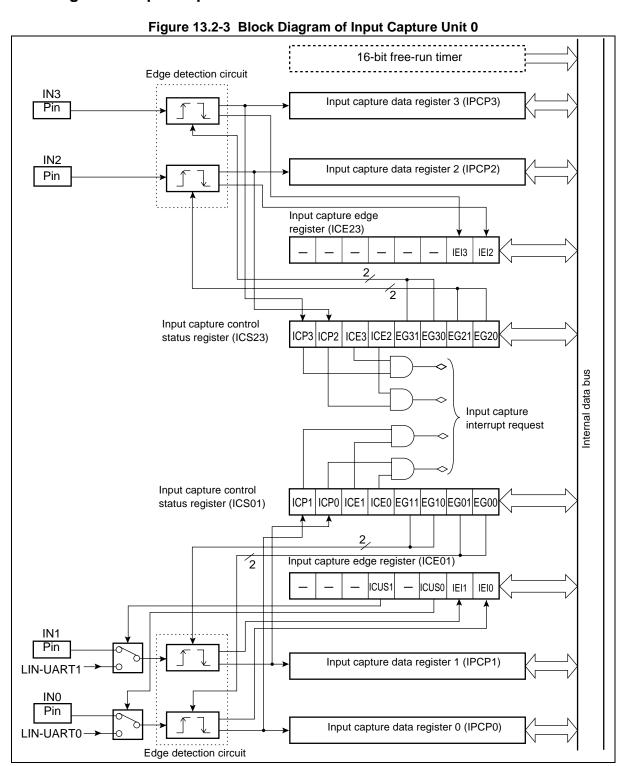

| CHAP | TER 12 WATCHDOG TIMER                                 | 195        |

| 12.1 |                                                       |            |

| 12.2 | •                                                     |            |

| 12.3 | •                                                     |            |

|      | .3.1 Watchdog timer control register (WDTC)           |            |

| 12.4 |                                                       |            |

| 12.5 | •                                                     |            |

| 12.6 |                                                       |            |

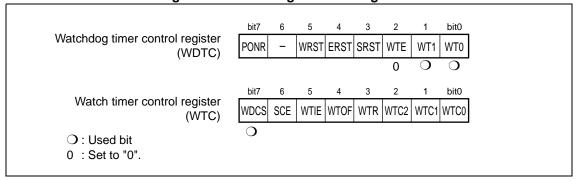

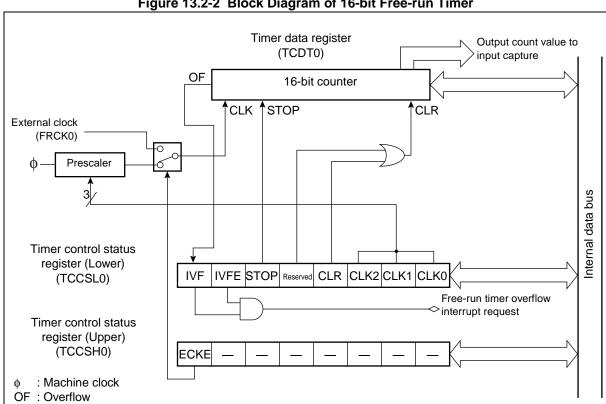

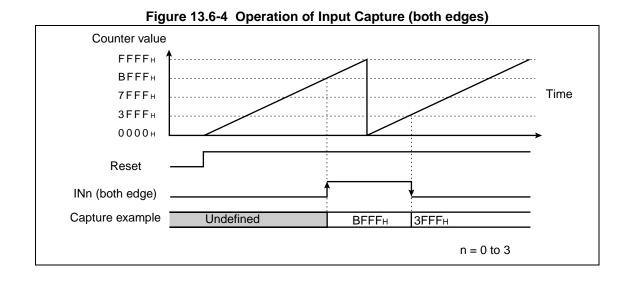

| CHAP | TER 13 16-Bit I/O TIMER                               | 209        |

| 13.1 |                                                       |            |

| 13.2 |                                                       |            |

|      | .2.1 Block Diagram of 16-bit Free-run Timer           |            |

|      | .2.2 Block Diagram of Input Capture                   |            |

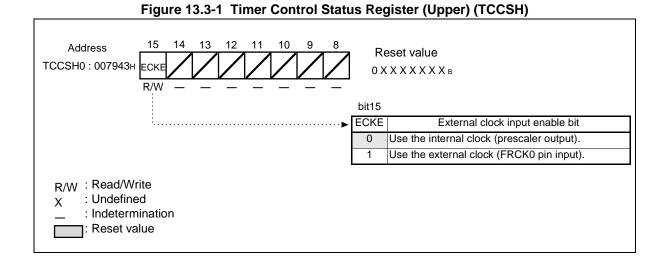

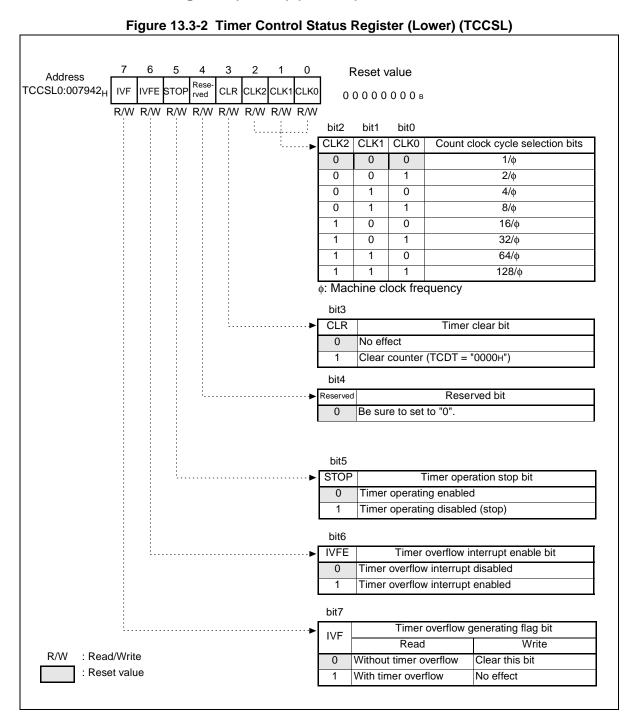

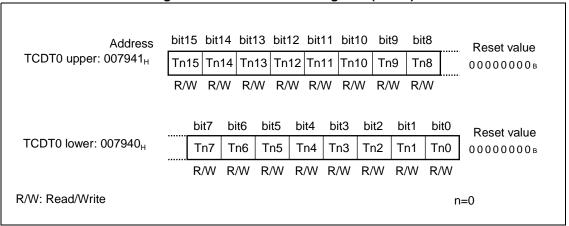

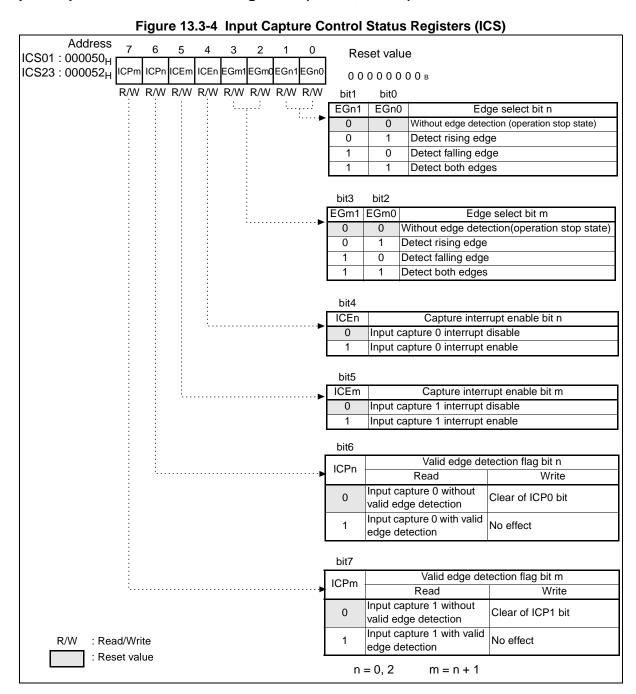

| 13.3 | • • •                                                 |            |

| 13.3 | -                                                     |            |

|      | .3.2 Timer Control Status Register (Lower) (TCCSL)    |            |

|      | .3.3 Timer Data Register (TCDT)                       |            |

|      | .3.4 Input Capture Control Status Registers (ICS)     |            |

|      | .3.5 Input Capture Register (IPCP)                    |            |

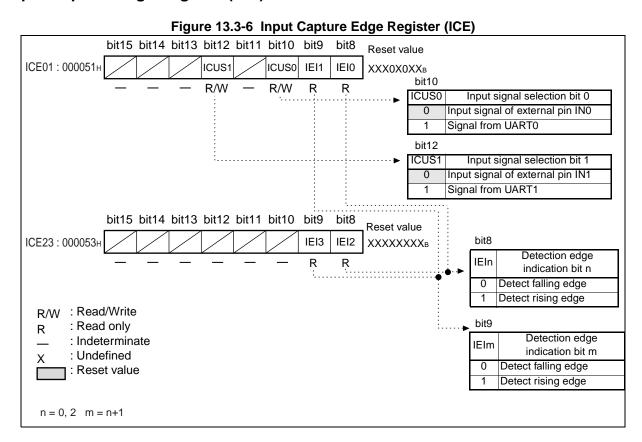

|      | .3.6 Input Capture Edge Register (ICE)                |            |

| 13.4 |                                                       |            |

| 10.7 |                                                       | ······ ∠∠1 |

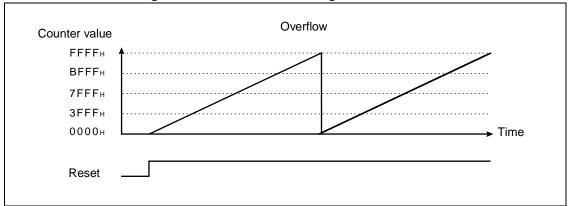

| 13.5  | Explanation of Operation of 16-bit Free-run Timer   | 229 |

|-------|-----------------------------------------------------|-----|

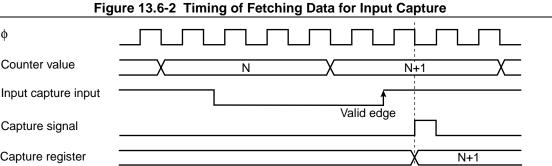

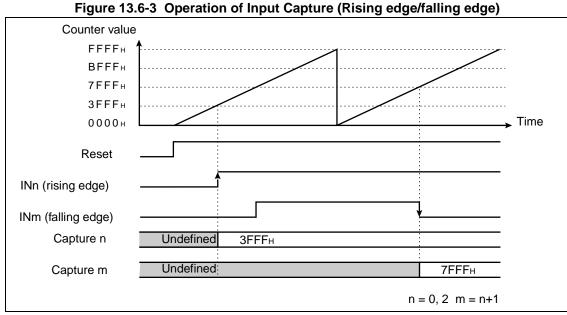

| 13.6  | Explanation of Operation of Input Capture           | 231 |

| 13.7  | Precautions when Using 16-bit I/O Timer             | 233 |

| 13.8  | Program Example of 16-bit I/O Timer                 | 234 |

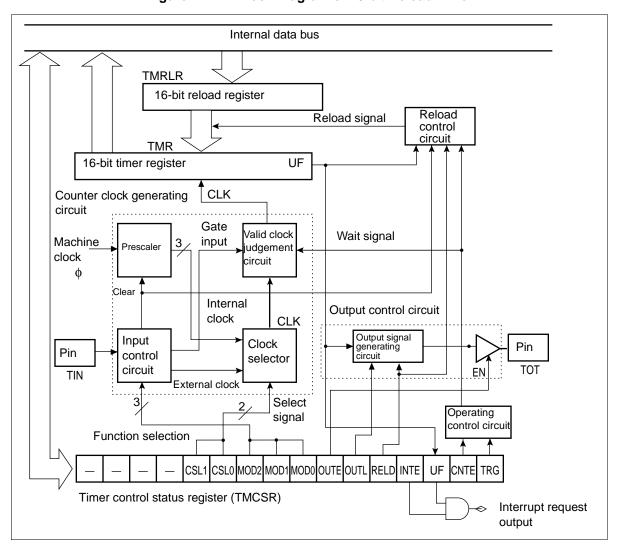

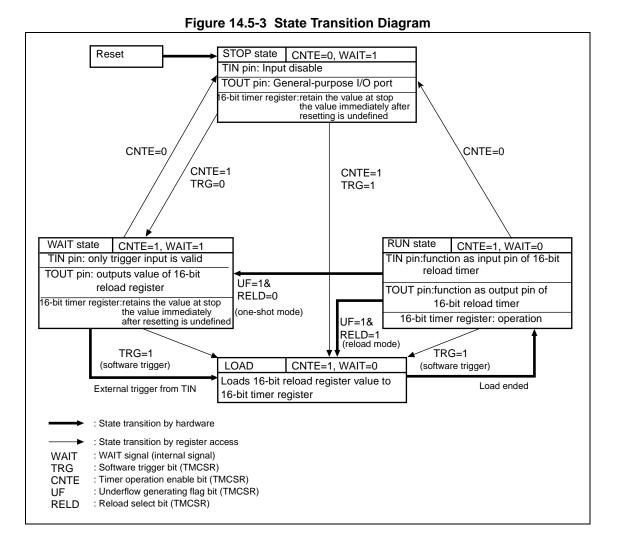

| СНАРТ | ER 14 16-BIT RELOAD TIMER                           | 237 |

| 14.1  | Overview of the 16-bit Reload Timer                 | 238 |

| 14.2  | Block Diagram of 16-bit Reload Timer                | 240 |

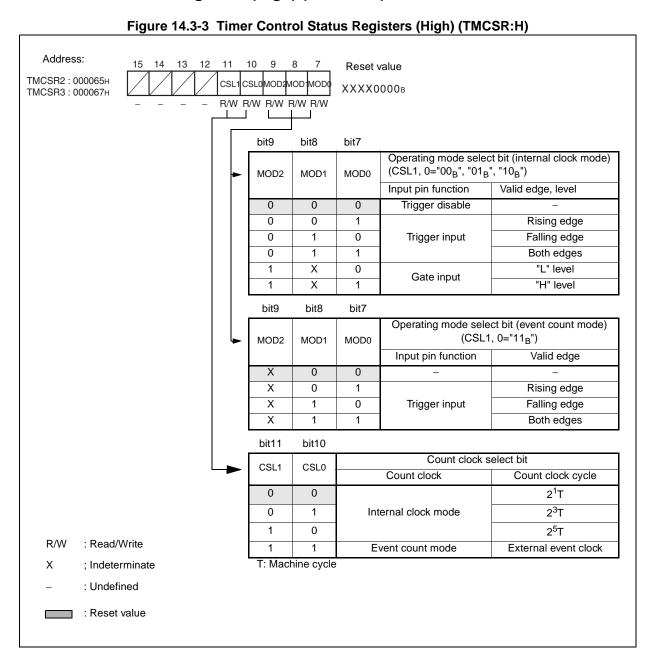

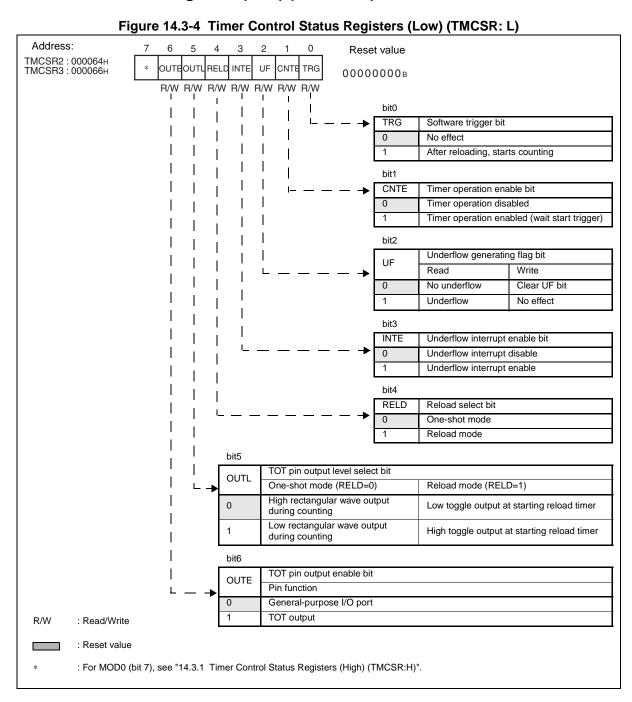

| 14.3  | Configuration of 16-bit Reload Timer                | 242 |

| 14.3  | 3.1 Timer Control Status Registers (High) (TMCSR:H) | 245 |

| 14.3  | 3.2 Timer Control Status Registers (Low) (TMCSR: L) | 247 |

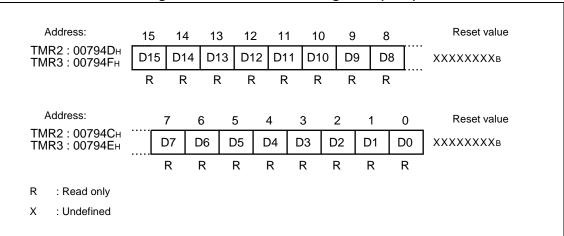

| 14.3  | 3.3 16-bit Timer Registers (TMR)                    | 249 |

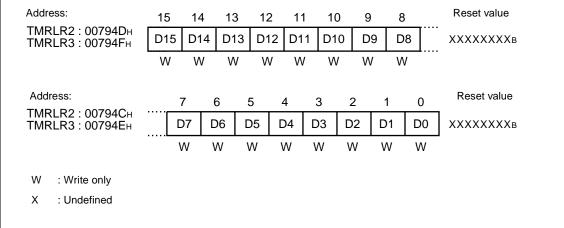

| 14.3  | 3.4 16-bit Reload Registers (TMRLR)                 | 250 |

| 14.4  | Interrupts of 16-bit Reload Timer                   | 251 |

| 14.5  | Explanation of Operation of 16-bit Reload Timer     | 252 |

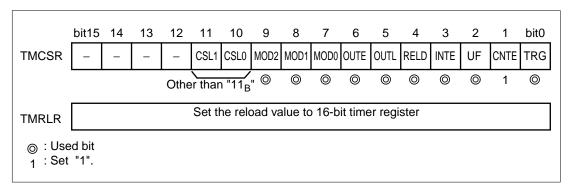

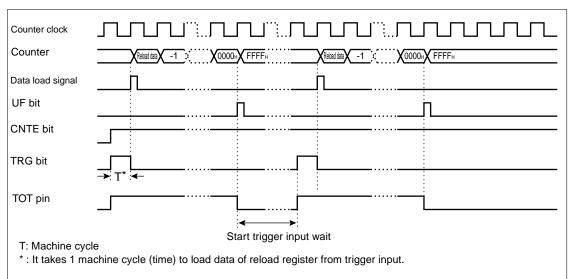

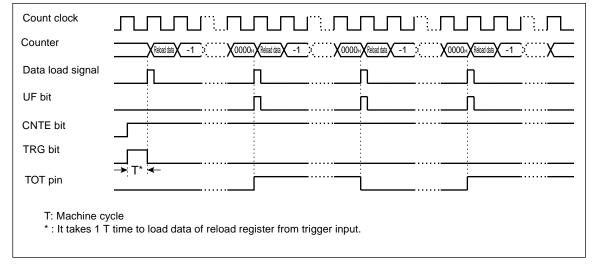

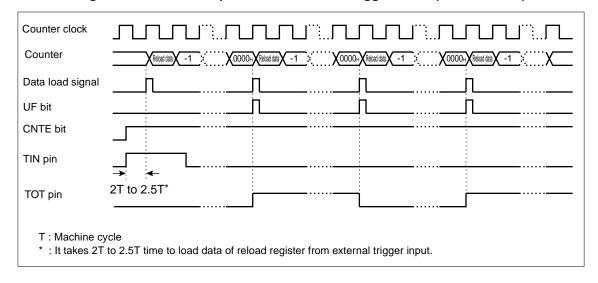

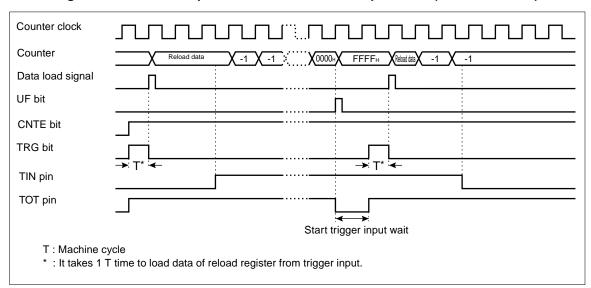

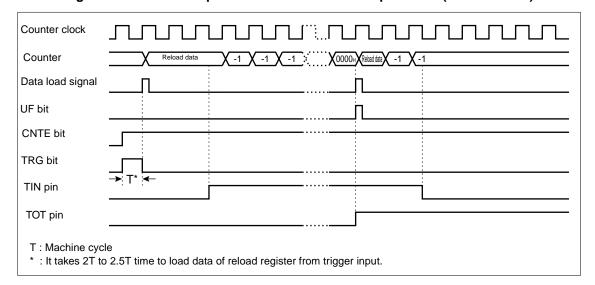

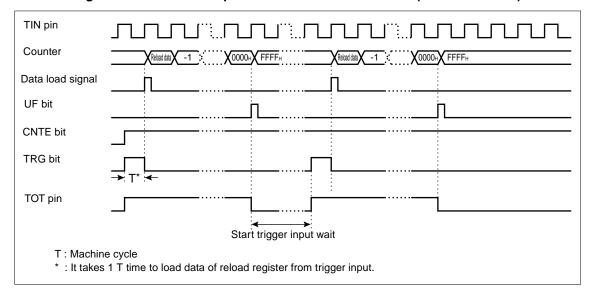

| 14.5  | 5.1 Operation in Internal Clock Mode                | 254 |

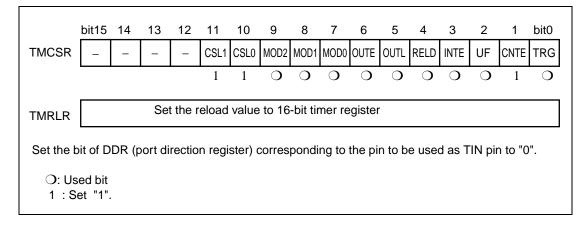

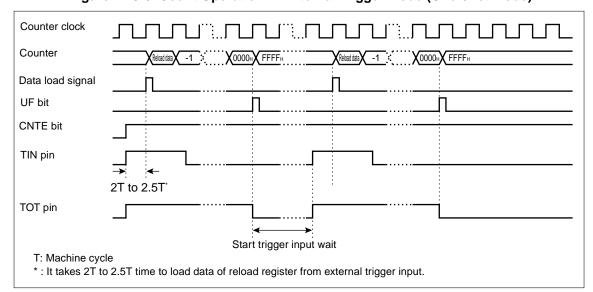

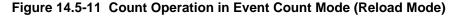

| 14.5  | 5.2 Operation in Event Count Mode                   | 259 |

| 14.6  | Precautions when Using 16-bit Reload Timer          | 262 |

| 14.7  | Sample Program of 16-bit Reload Timer               | 263 |

| СНАРТ | TER 15 WATCH TIMER                                  | 267 |

| 15.1  | Overview of Watch Timer                             | 268 |

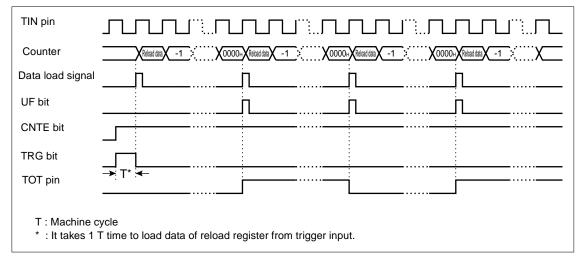

| 15.2  | Block Diagram of Watch Timer                        | 270 |

| 15.3  | Configuration of Watch Timer                        | 272 |

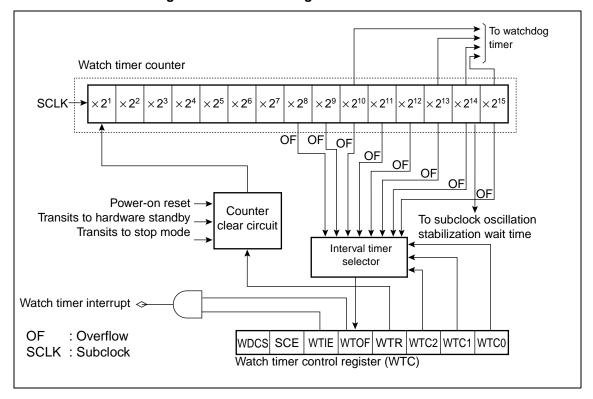

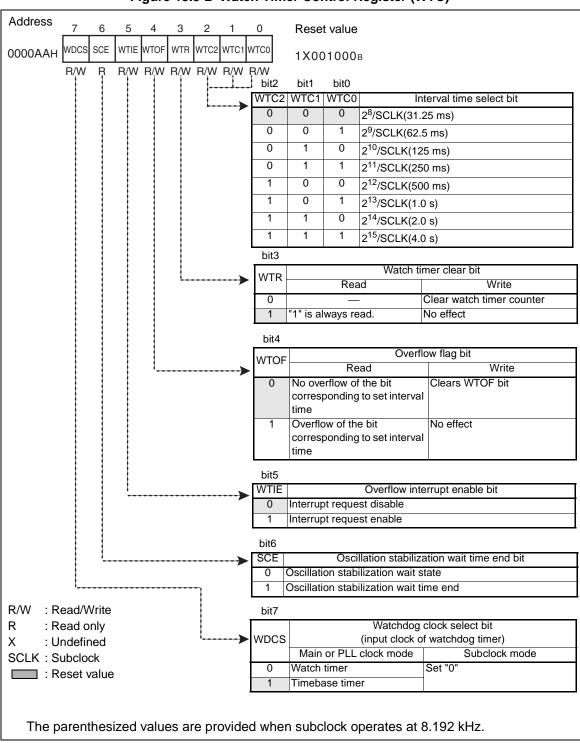

| 15.3  | 3.1 Watch Timer Control Register (WTC)              | 273 |

| 15.4  | Watch Timer Interrupt                               | 275 |

| 15.5  | Explanation of Operation of Watch Timer             | 276 |

| 15.6  | Program Example of Watch Timer                      | 278 |

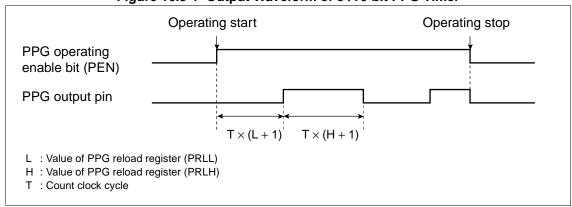

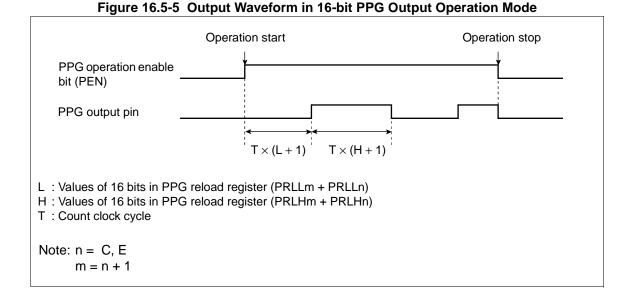

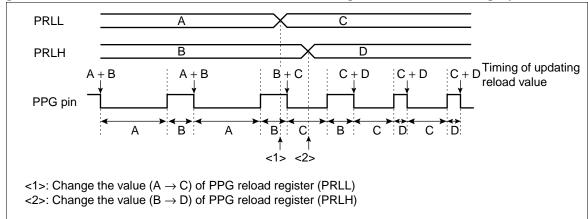

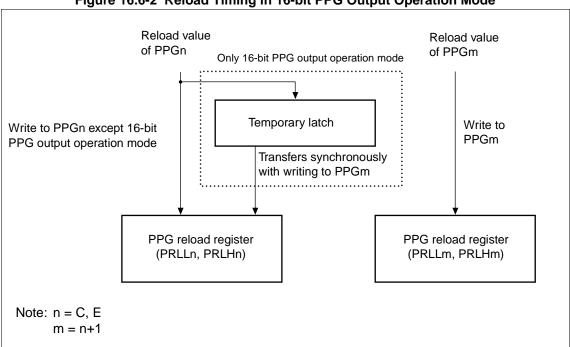

| СНАРТ | ER 16 8-/16-BIT PPG TIMER                           | 281 |

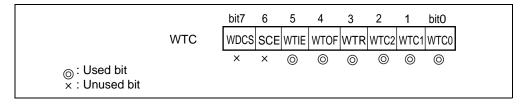

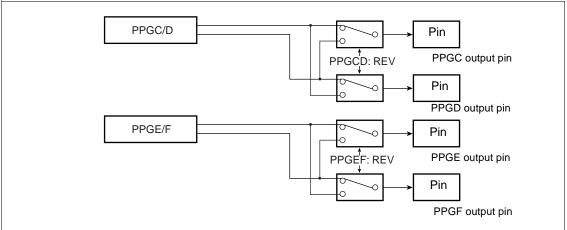

| 16.1  | Overview of 8-/16-bit PPG Timer                     | 282 |

| 16.2  | Block Diagram of 8-/16-bit PPG Timer                |     |

| 16.2  | -                                                   |     |

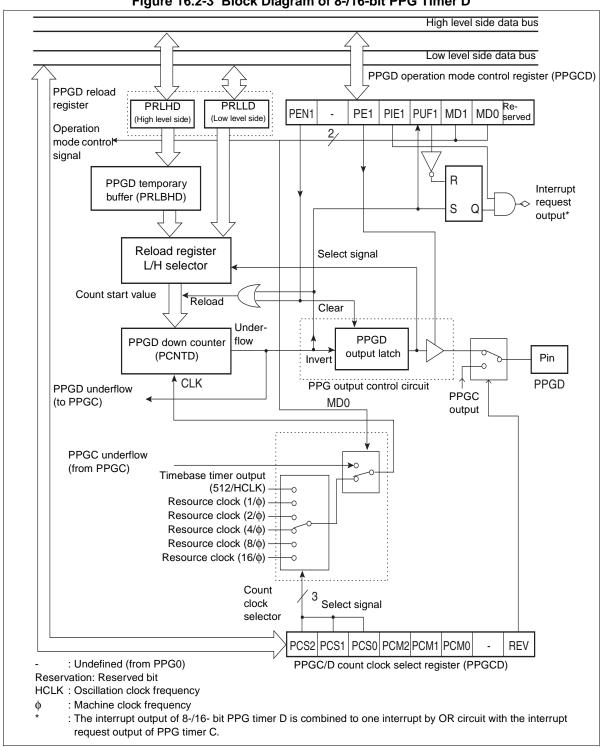

| 16.2  | 2.2 Block Diagram of 8-/16-bit PPG Timer D          | 288 |

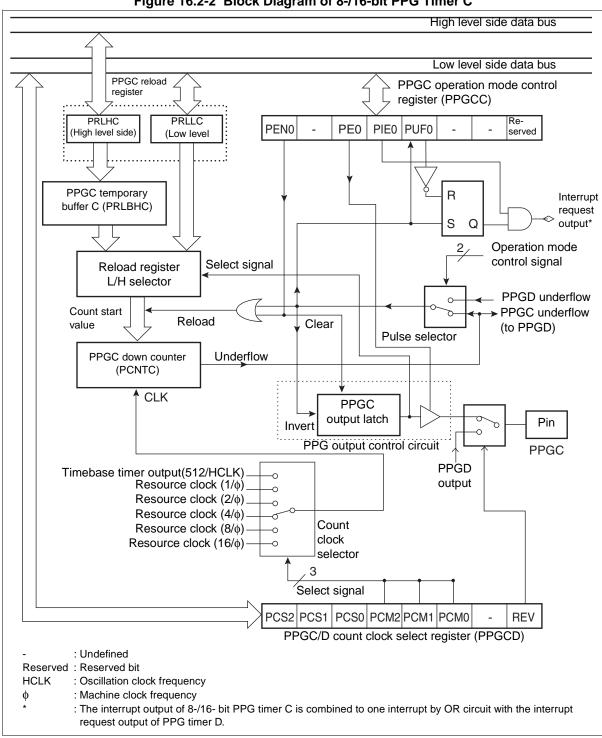

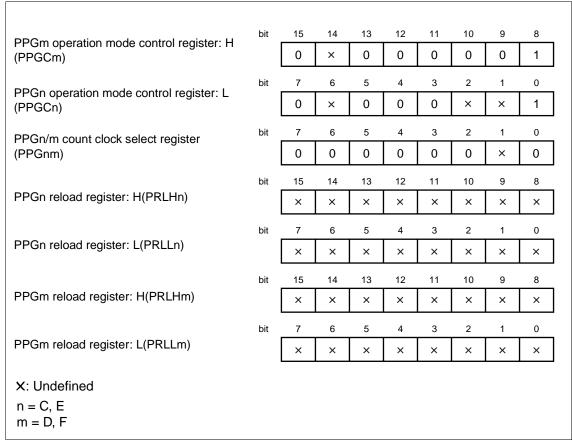

| 16.3  | Configuration of 8-/16-bit PPG Timer                |     |

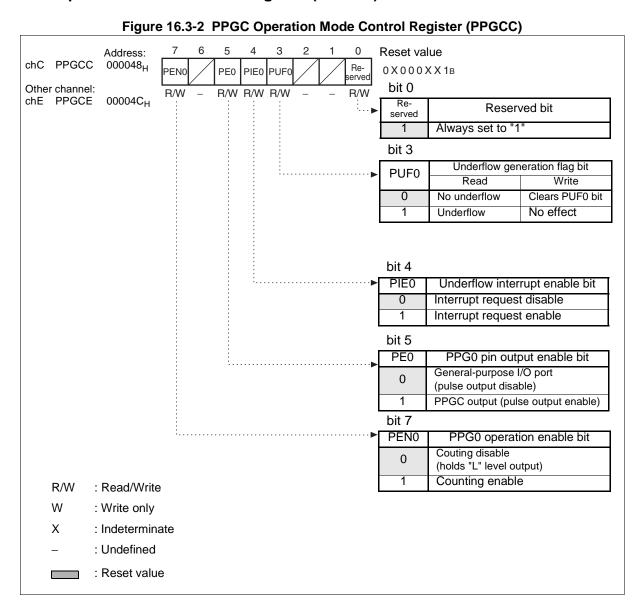

| 16.3  | 3.1 PPGC Operation Mode Control Register (PPGCC)    | 292 |

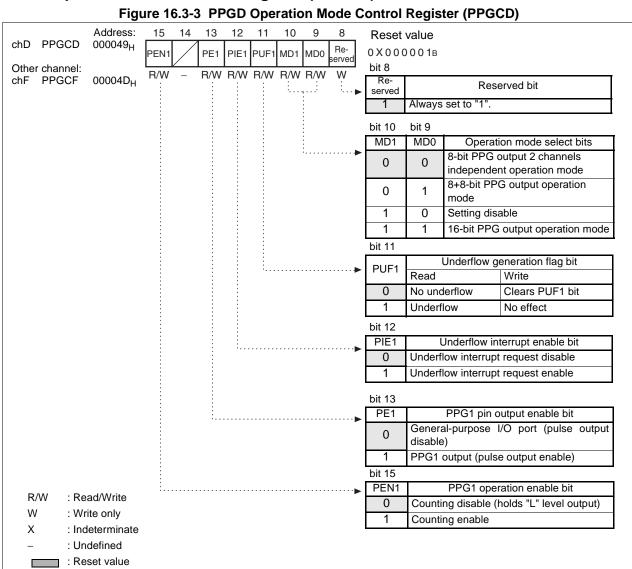

| 16.3  | 3.2 PPGD Operation Mode Control Register (PPGCD)    | 294 |

| 16.3  | 3.3 PPGC/D Count Clock Select Register (PPGCD)      | 296 |

| 16.3  | 3.4 PPG Reload Registers (PRLLC/PRLHC, PRLLD/PRLHD) | 298 |

| 16.4  | Interrupts of 8-/16-bit PPG Timer                   |     |

| 16.5  | Explanation of Operation of 8-/16-bit PPG Timer     |     |

| 16.5  | ·                                                   |     |

| 16.5  | ·                                                   |     |

| 16.5  | ·                                                   |     |

|       | Precautions when Using 8-/16-bit PPG Timer          |     |

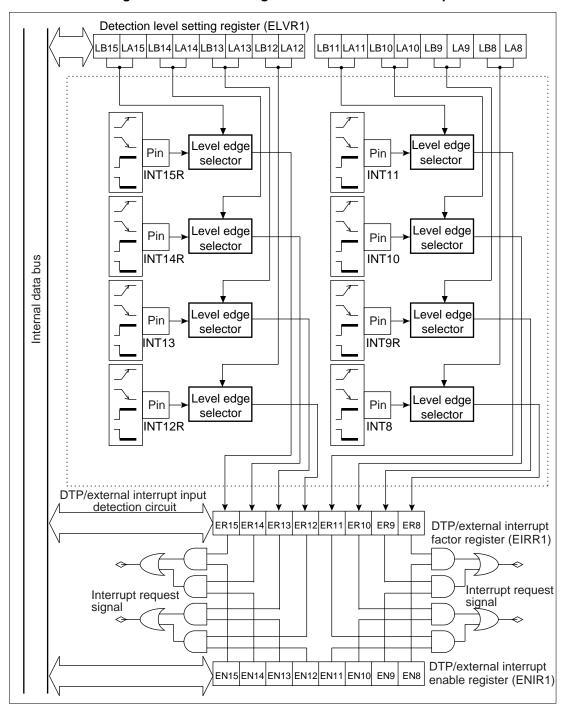

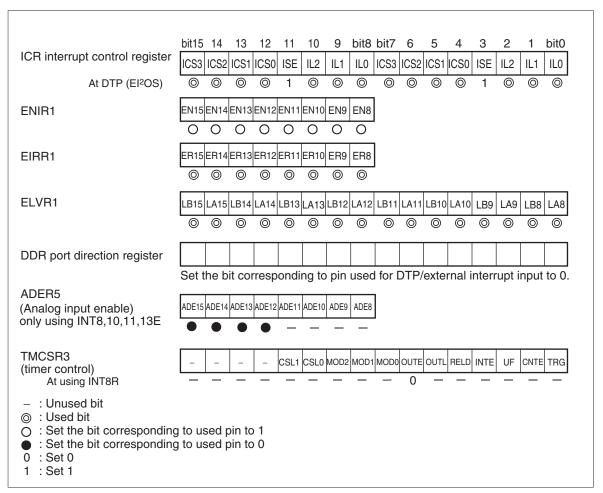

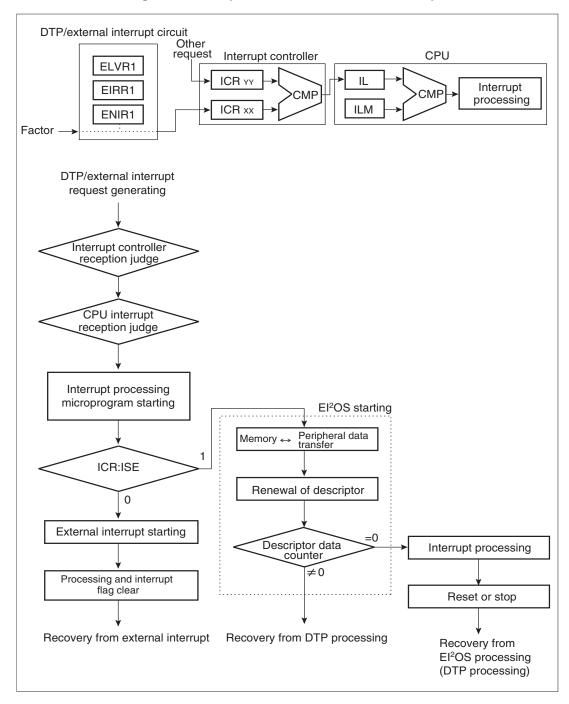

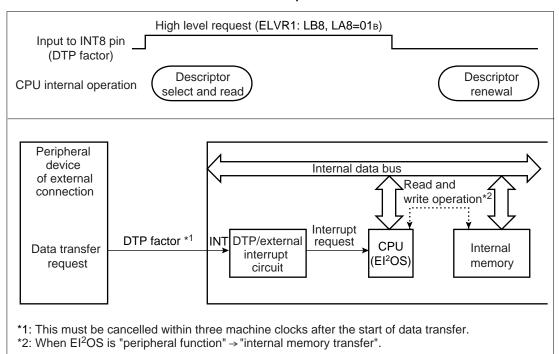

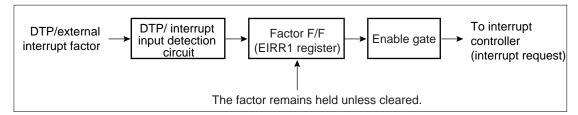

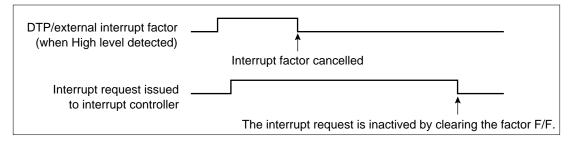

| CHAPT | ER 17 DTP/EXTERNAL INTERRUPTS                                        | 313 |

|-------|----------------------------------------------------------------------|-----|

| 17.1  | Overview of DTP/External Interrupt                                   | 314 |

| 17.2  | Block Diagram of DTP/External Interrupt                              | 315 |

| 17.3  | Configuration of DTP/External Interrupt                              | 317 |

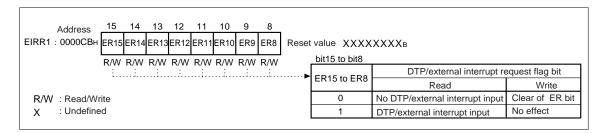

| 17.3  | 3.1 DTP/External Interrupt Factor Register (EIRR1)                   | 319 |

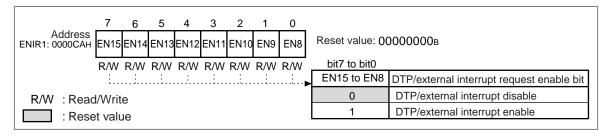

| 17.3  | 3.2 DTP/External Interrupt Enable Register (ENIR1)                   | 321 |

| 17.3  | B.3 Detection Level Setting Register (ELVR1)                         | 323 |

| 17.3  | 8.4 External Interrupt Factor Select Register (EISSR)                | 325 |

| 17.4  | Explanation of Operation of DTP/External Interrupt                   | 327 |

| 17.4  | l.1 External Interrupt Function                                      | 331 |

| 17.4  | I.2 DTP Function                                                     | 332 |

| 17.5  | Precautions when Using DTP/External Interrupt                        | 333 |

| 17.6  | Program Example of DTP/External Interrupt Function                   | 335 |

| СНАРТ | ER 18 8-/10-BIT A/D CONVERTER                                        | 339 |

| 18.1  | Overview of 8-/10-bit A/D Converter                                  |     |

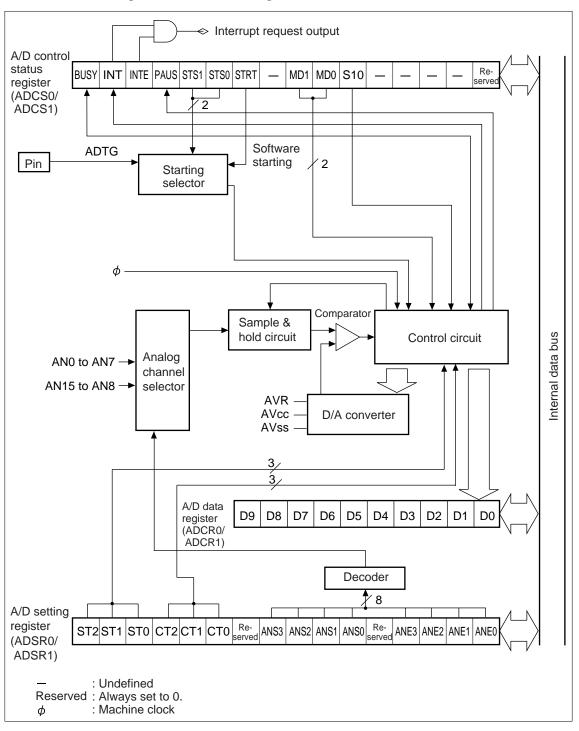

| 18.2  | Block Diagram of 8-/10-bit A/D Converter                             | 341 |

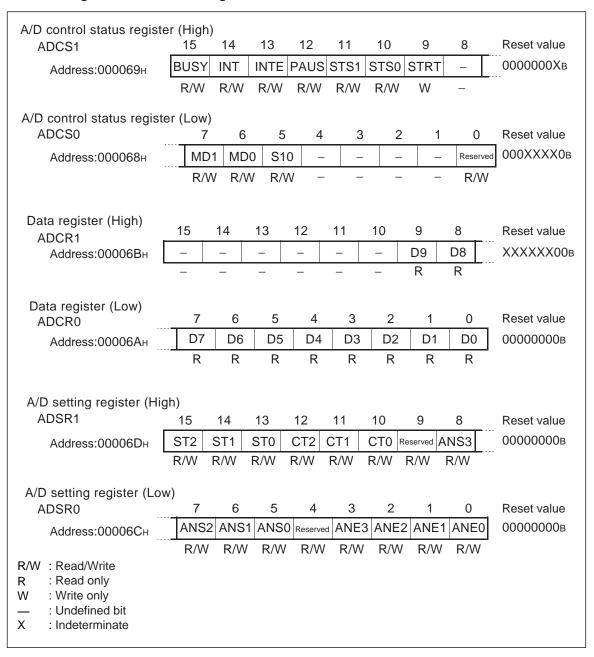

| 18.3  | Configuration of 8-/10-bit A/D Converter                             | 344 |

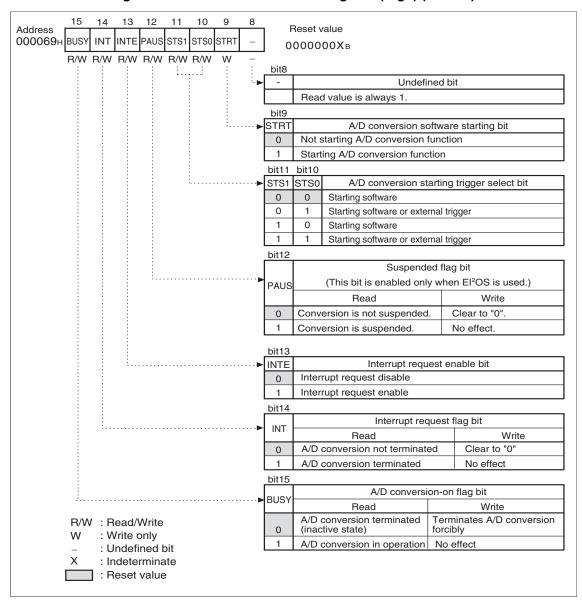

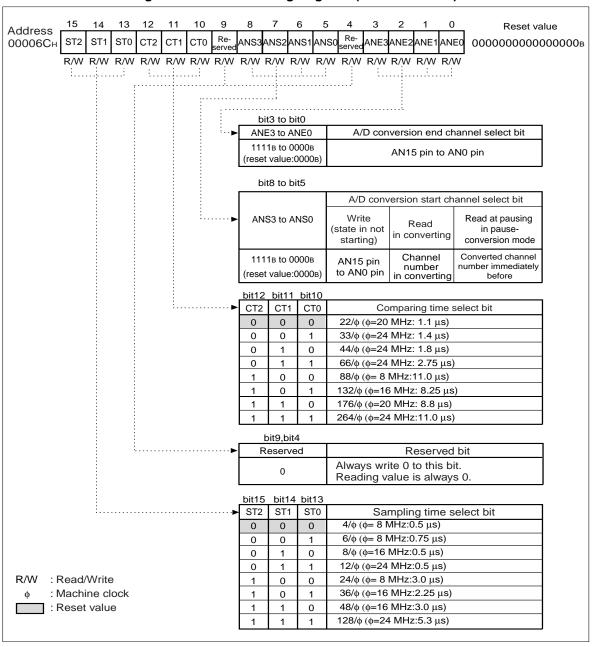

| 18.3  | 3.1 A/D Control Status Register (High) (ADCS1)                       | 346 |

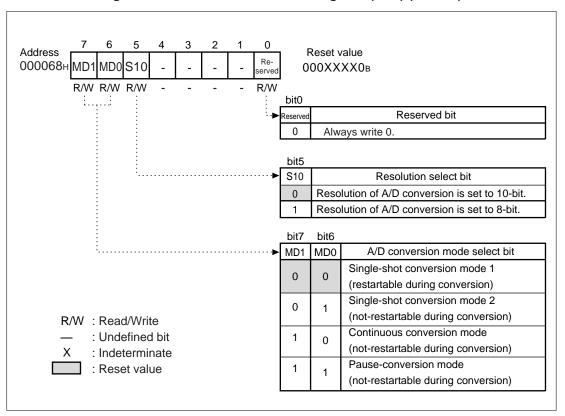

| 18.3  | 3.2 A/D Control Status Register (Low) (ADCS0)                        | 349 |

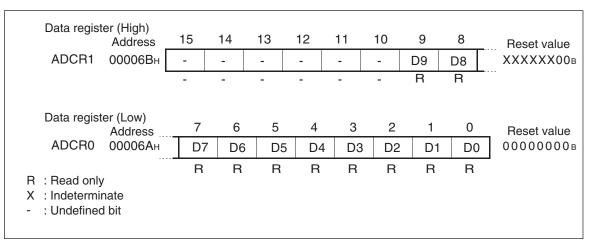

| 18.3  | 3.3 A/D Data Register (ADCR0/ADCR1)                                  | 351 |

| 18.3  | 3.4 A/D Setting Register (ADSR0/ADSR1)                               | 352 |

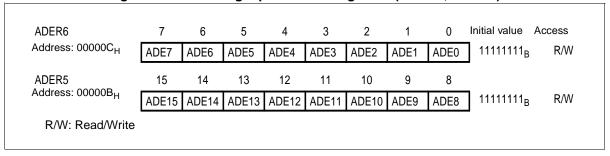

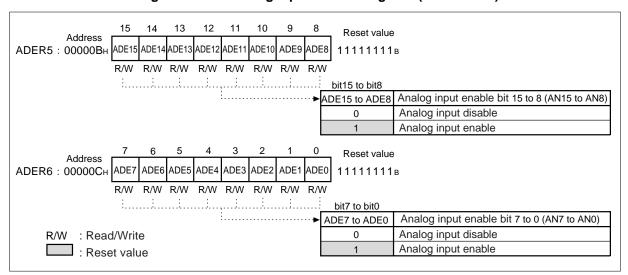

| 18.3  | 3.5 Analog Input Enable Register (ADER5, ADER6)                      | 356 |

| 18.4  | Interrupt of 8-/10-bit A/D Converter                                 | 358 |

| 18.5  | Explanation of Operation of 8-/10-bit A/D Converter                  | 359 |

| 18.5  | 5.1 Single-shot Conversion Mode                                      | 360 |

| 18.5  | 5.2 Continuous Conversion Mode                                       | 362 |

| 18.5  | i.3 Pause-conversion Mode                                            | 364 |

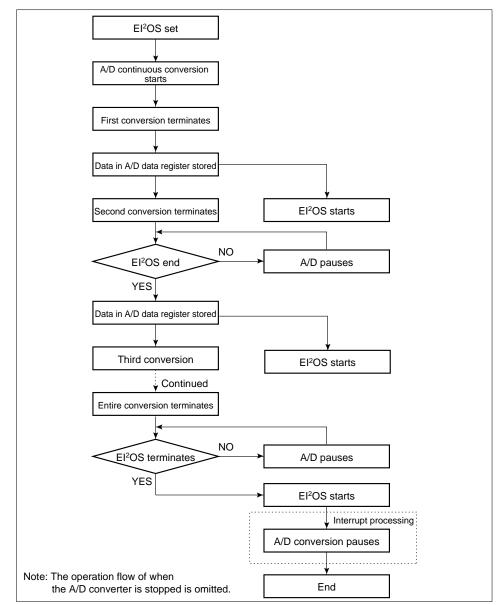

| 18.5  | 5.4 Conversion Using El <sup>2</sup> OS Function                     | 366 |

| 18.5  | 5.5 A/D-converted Data Protection Function                           | 367 |

| 18.6  | Precautions when Using 8-/10-bit A/D Converter                       | 369 |

| СНАРТ | ER 19 LOW VOLTAGE DETECTION/CPU OPERATING DETECTION RESE             | ĒΤ  |

|       |                                                                      | 371 |

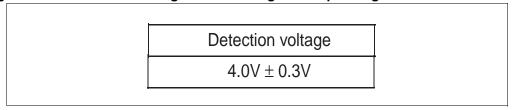

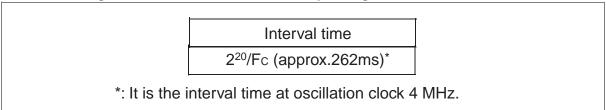

| 19.1  | Overview of Low Voltage/CPU Operating Detection Reset Circuit        |     |

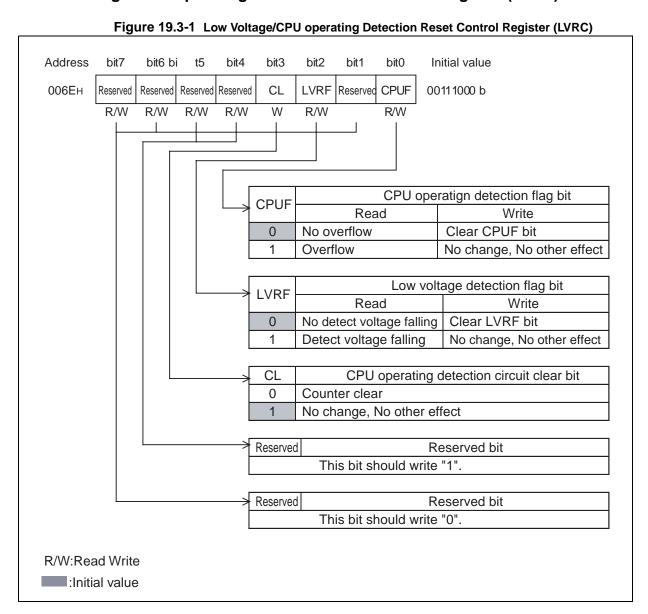

| 19.2  | Configuration of Low Voltage/CPU Operating Detection Reset Circuit   | 374 |

| 19.3  | Low Voltage/CPU Operating Detection Reset Circuit Register           |     |

| 19.4  | Operating of Low Voltage/CPU Operating Detection Reset Circuit       | 378 |

| 19.5  | Notes on Using Low Voltage/CPU Operating Detection Reset Circuit     | 379 |

| 19.6  | Sample Program for Low Voltage/CPU Operating Detection Reset Circuit | 380 |

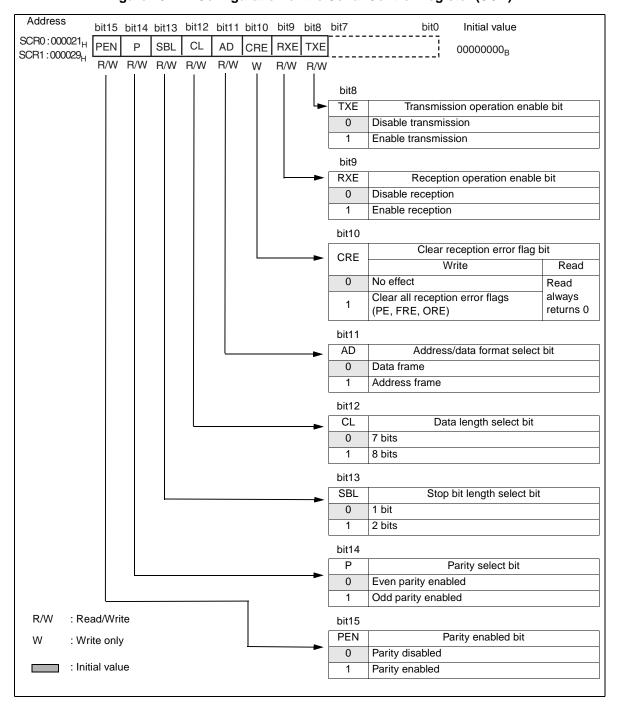

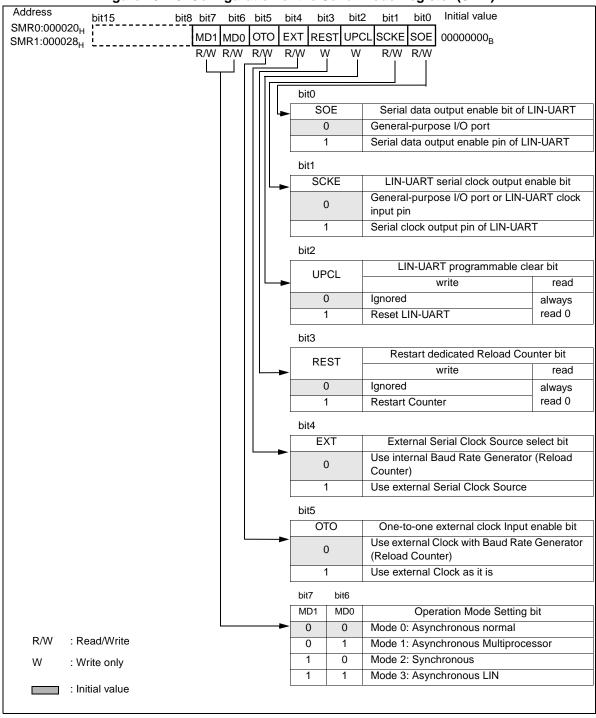

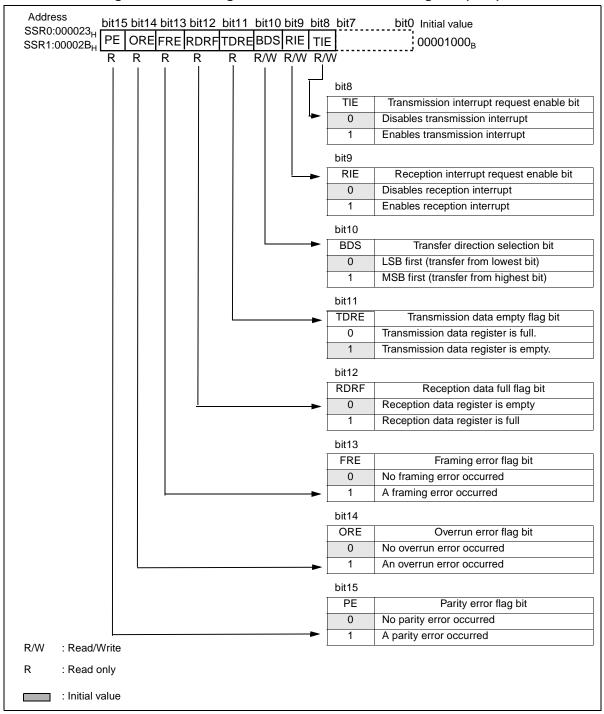

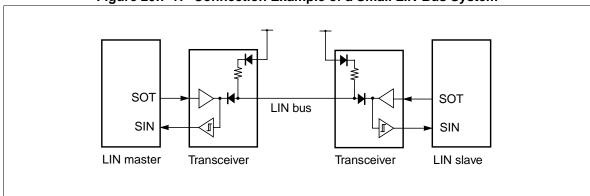

| СНАРТ | ER 20 LIN-UART                                                       | 381 |

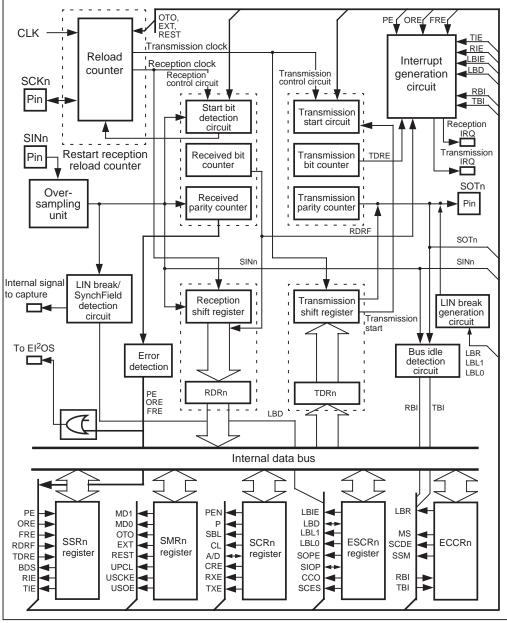

| 20.1  | Overview of LIN-UART                                                 | 382 |

| 20.2  | Configuration of LIN-UART                                            | 386 |

| 20.3  | LIN-UART Pins                                                        | 391 |

| 20.4  | LIN-UART Registers                                                   | 392 |

| 20.4  | l.1 Serial Control Register (SCR)                                    | 393 |

|                                                                                                                                                                        | LIN-UART Serial Mode Register (SMR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 20.4.3                                                                                                                                                                 | Serial Status Register (SSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 397        |

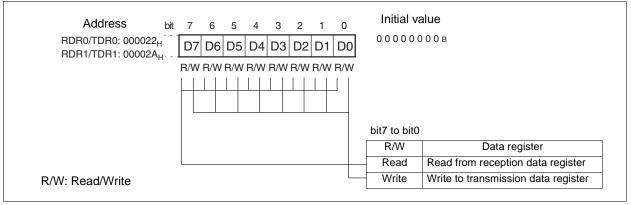

| 20.4.4                                                                                                                                                                 | Reception and Transmission Data Register (RDR/TDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 399        |

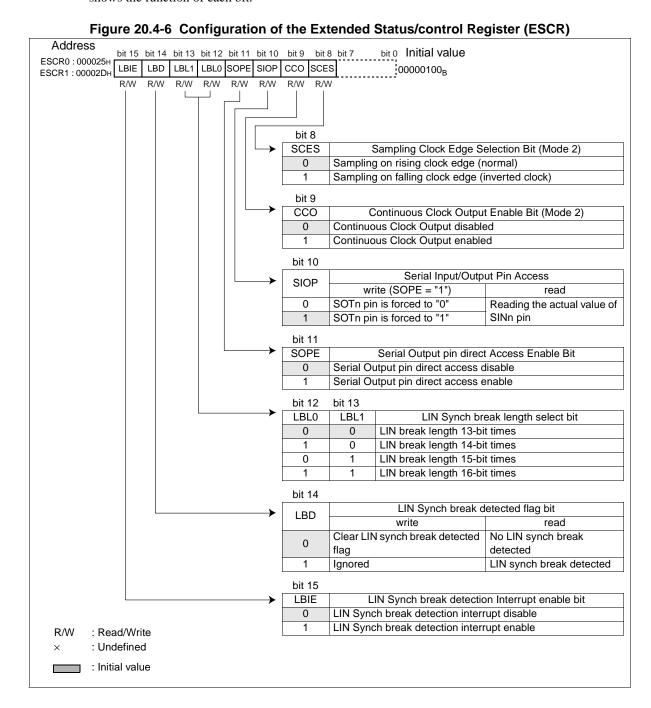

| 20.4.5                                                                                                                                                                 | Extended Status/Control Register (ESCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 401        |

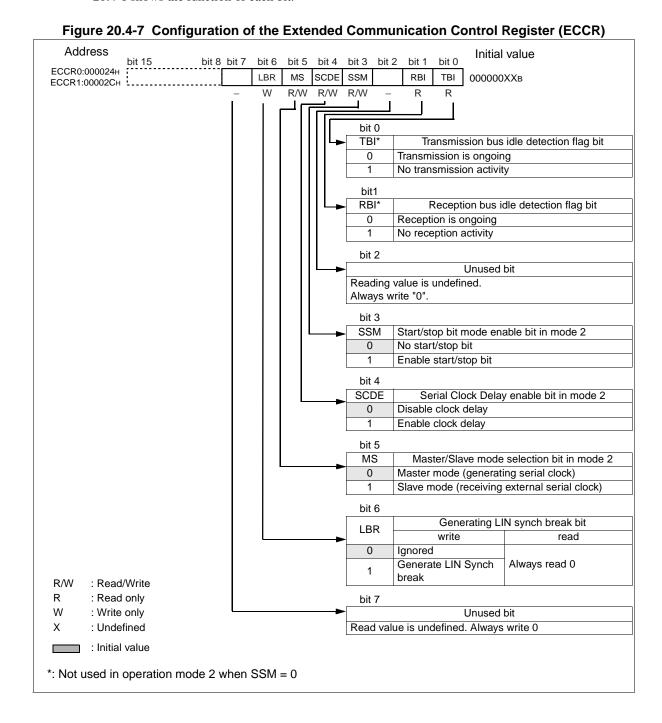

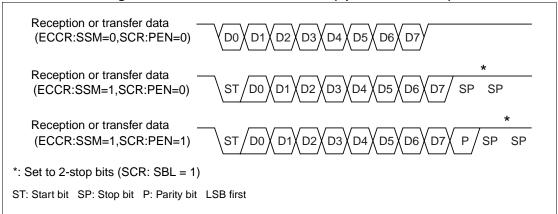

| 20.4.6                                                                                                                                                                 | Extended Communication Control Register (ECCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 403        |

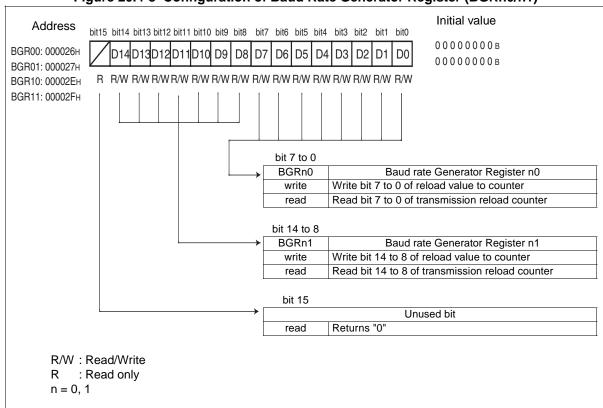

| 20.4.7                                                                                                                                                                 | Baud Rate Generator Register 0 and 1 (BGR0/1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 405        |

| 20.5 LI                                                                                                                                                                | N-UART Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 406        |

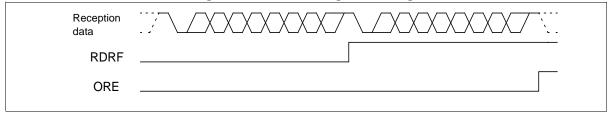

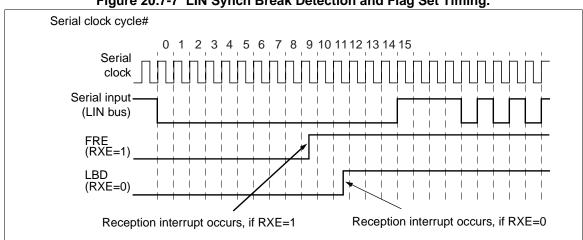

| 20.5.1                                                                                                                                                                 | Reception Interrupt Generation and Flag Set Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 409        |

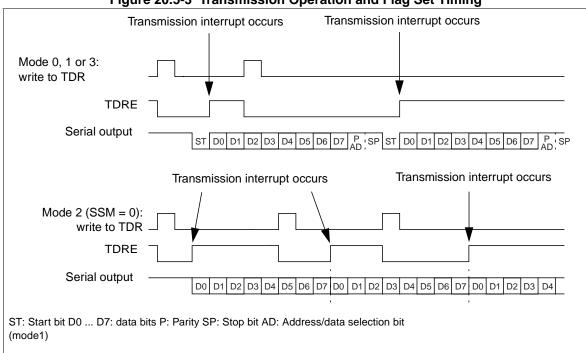

| 20.5.2                                                                                                                                                                 | Transmission Interrupt Generation and Flag Set Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 411        |

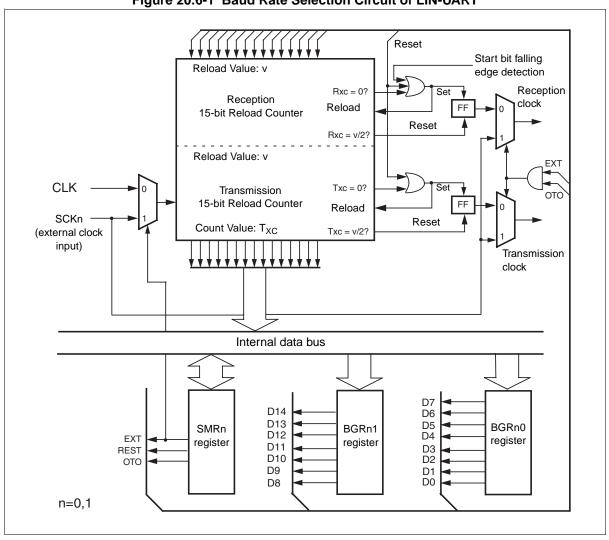

| 20.6 LI                                                                                                                                                                | N-UART Baud Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 413        |

| 20.6.1                                                                                                                                                                 | Setting the Baud Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 415        |

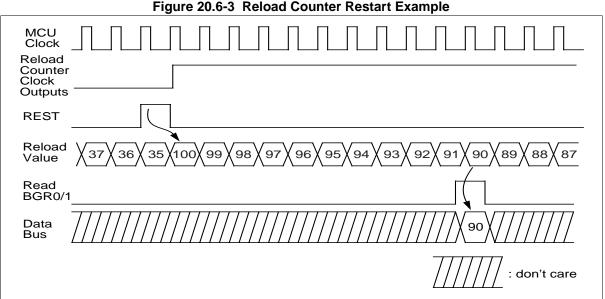

| 20.6.2                                                                                                                                                                 | Restarting the Reload Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 418        |

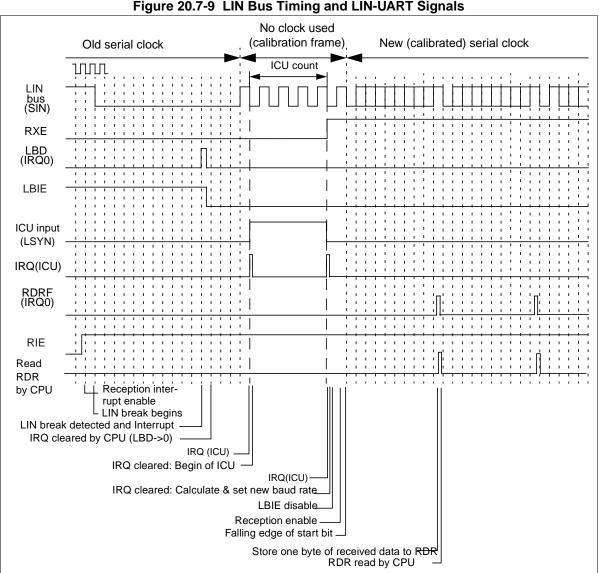

| 20.7 O                                                                                                                                                                 | peration of LIN-UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 420        |

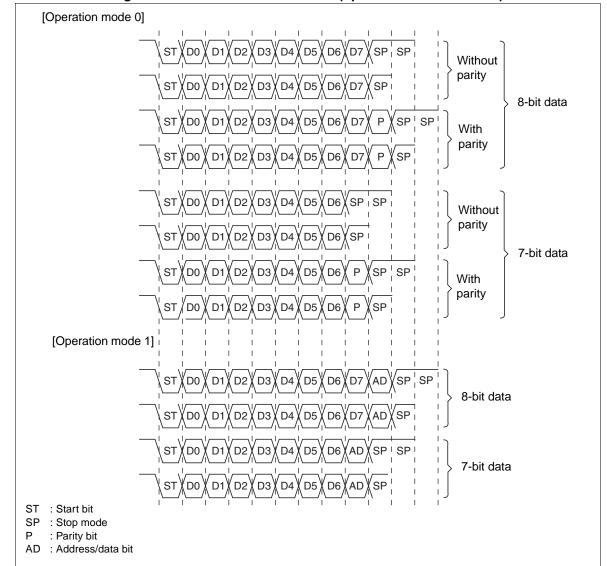

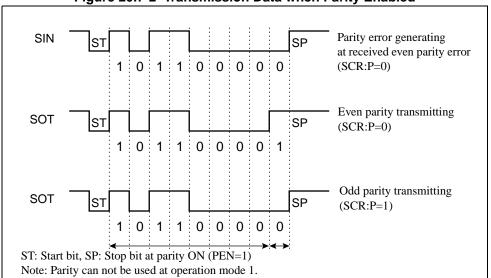

| 20.7.1                                                                                                                                                                 | Operation in Asynchronous Mode (Op. Modes 0 and 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 422        |

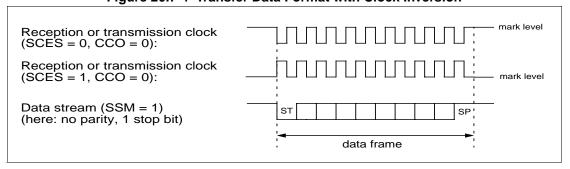

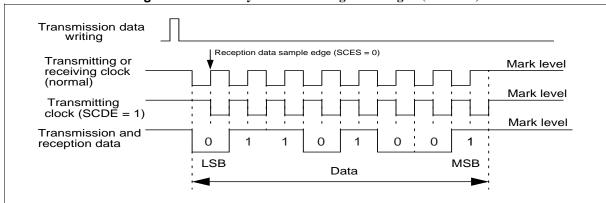

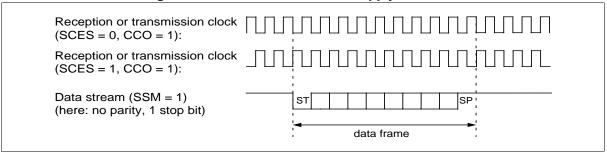

| 20.7.2                                                                                                                                                                 | Operation in Synchronous Mode (Operation Mode 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 426        |

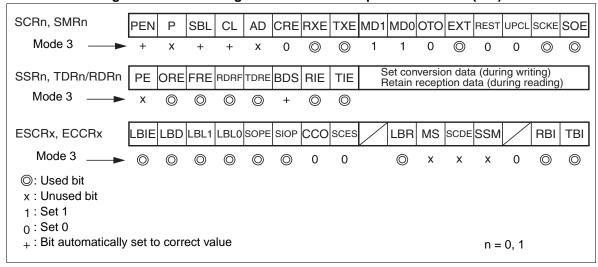

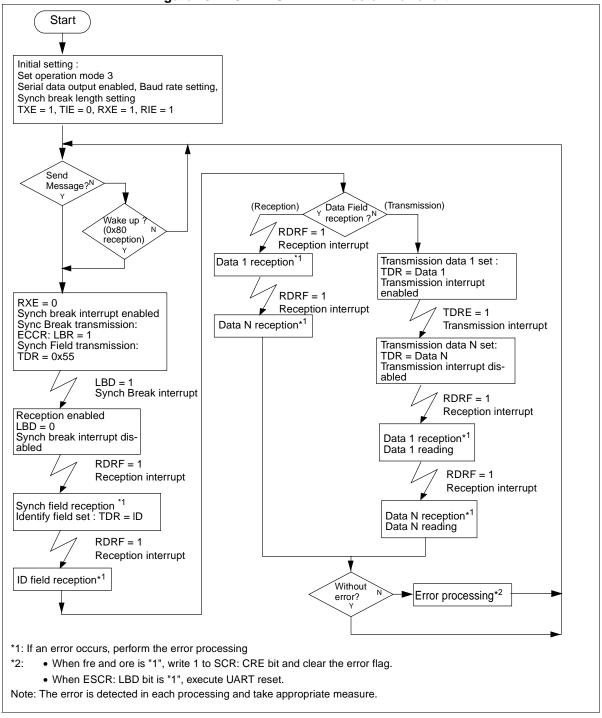

| 20.7.3                                                                                                                                                                 | Operation with LIN Function (Operation Mode 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 429        |

| 20.7.4                                                                                                                                                                 | Direct Access to Serial Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 432        |

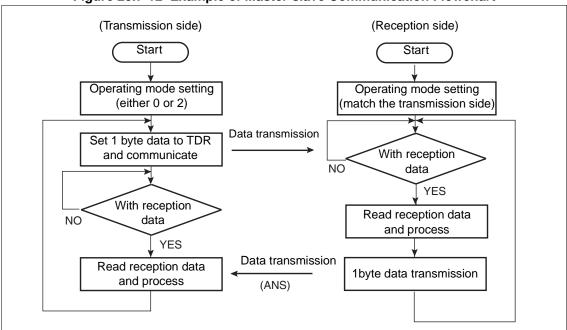

| 20.7.5                                                                                                                                                                 | Bidirectional Communication Function (Normal Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 433        |

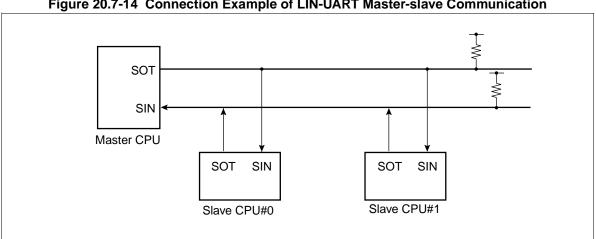

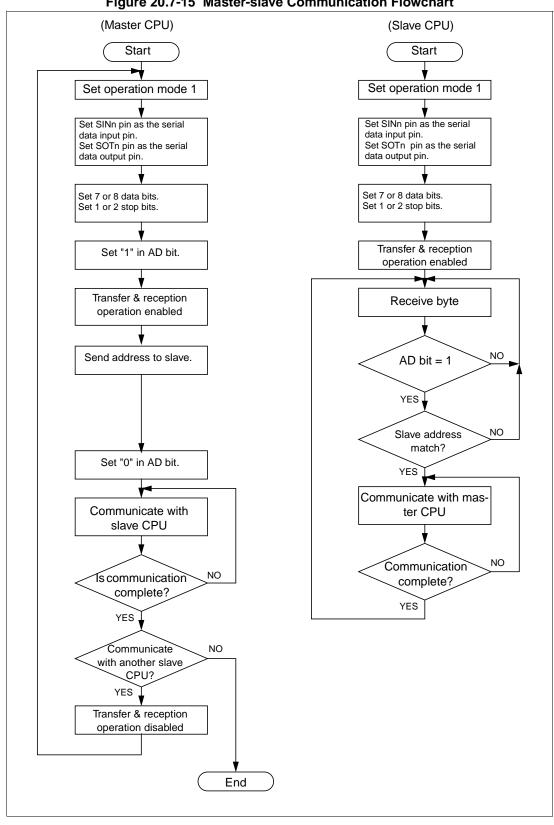

| 20.7.6                                                                                                                                                                 | Master-Slave Communication Function (Multiprocessor Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 435        |

| 20.7.7                                                                                                                                                                 | LIN Communication Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 438        |

| 20.7.8                                                                                                                                                                 | Sample Flowcharts for LIN-UART in LIN communication (Operation Mode 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 439        |

| 20.8 N                                                                                                                                                                 | otes on Using LIN-UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 441        |

|                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

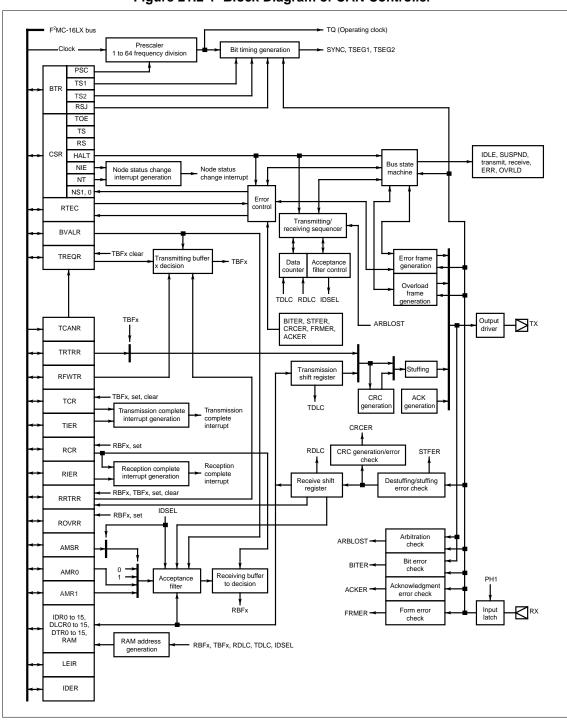

| CHAPTER                                                                                                                                                                | 21 CAN CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 443        |

|                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

| 21.1 Fe                                                                                                                                                                | eatures of CAN Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 444        |

|                                                                                                                                                                        | eatures of CAN Controllerock Diagram of CAN Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| 21.2 BI                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 445        |

| 21.2 Bl<br>21.3 Li                                                                                                                                                     | ock Diagram of CAN Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 445<br>446 |

| 21.2 Bl<br>21.3 Li                                                                                                                                                     | ock Diagram of CAN Controllerst of Overall Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

| 21.2 Bl<br>21.3 Li<br>21.4 C                                                                                                                                           | ock Diagram of CAN Controllerst of Overall Control Registerslassifying CAN Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

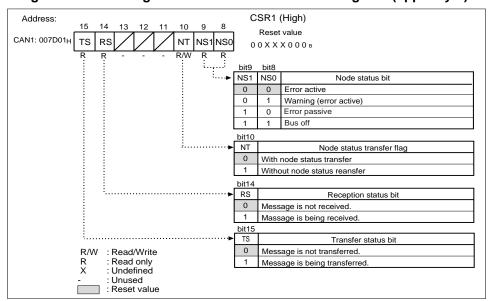

| 21.2 BI<br>21.3 Li<br>21.4 C<br>21.4.1                                                                                                                                 | ock Diagram of CAN Controllerst of Overall Control Registerslassifying CAN Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

| 21.2 Bl<br>21.3 Li<br>21.4 Cl<br>21.4.1<br>21.4.2                                                                                                                      | ock Diagram of CAN Controller st of Overall Control Registers lassifying CAN Controller Registers Configuration of Control Status Register (CSR) Function of Control Status Register (CSR) Correspondence between Node Status Bit and Node Status Notes on Using Bus Operation Stop Bit (HALT = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| 21.2 BI<br>21.3 Li<br>21.4 C<br>21.4.1<br>21.4.2<br>21.4.3                                                                                                             | ock Diagram of CAN Controller st of Overall Control Registers lassifying CAN Controller Registers Configuration of Control Status Register (CSR) Function of Control Status Register (CSR) Correspondence between Node Status Bit and Node Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

| 21.2 Bl<br>21.3 Li<br>21.4 Cl<br>21.4.1<br>21.4.2<br>21.4.3<br>21.4.4                                                                                                  | ock Diagram of CAN Controller st of Overall Control Registers lassifying CAN Controller Registers Configuration of Control Status Register (CSR) Function of Control Status Register (CSR) Correspondence between Node Status Bit and Node Status Notes on Using Bus Operation Stop Bit (HALT = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| 21.2 Bl<br>21.3 Li<br>21.4 Cl<br>21.4.1<br>21.4.2<br>21.4.3<br>21.4.4<br>21.4.5                                                                                        | lock Diagram of CAN Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

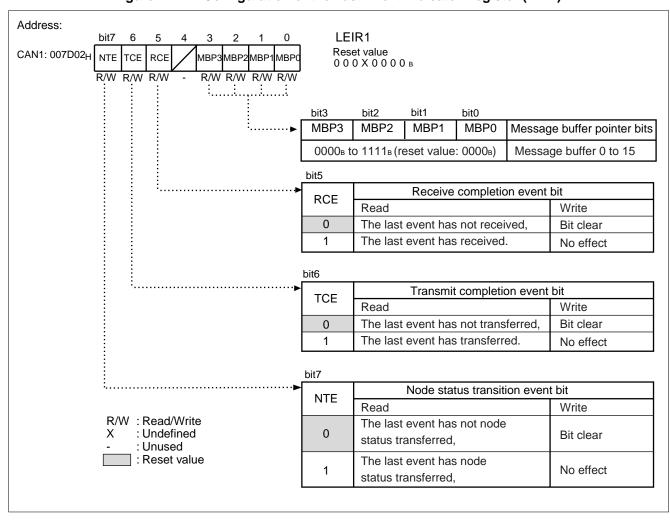

| 21.2 Bl<br>21.3 Li<br>21.4 Cl<br>21.4.1<br>21.4.2<br>21.4.3<br>21.4.4<br>21.4.5<br>21.4.6                                                                              | ock Diagram of CAN Controller st of Overall Control Registers lassifying CAN Controller Registers Configuration of Control Status Register (CSR) Function of Control Status Register (CSR) Correspondence between Node Status Bit and Node Status Notes on Using Bus Operation Stop Bit (HALT = 1) Last Event Indicator Register (LEIR) Receive and Transmit Error Counters (RTEC)                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

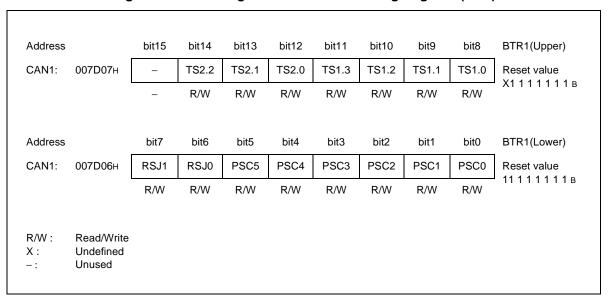

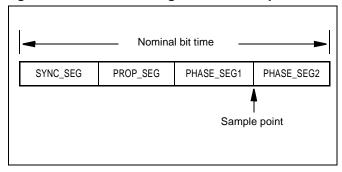

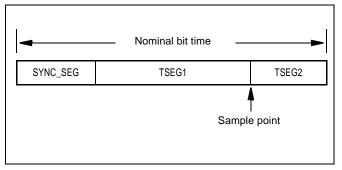

| 21.2 Bl<br>21.3 Li<br>21.4 C<br>21.4.1<br>21.4.2<br>21.4.3<br>21.4.4<br>21.4.5<br>21.4.6<br>21.4.7<br>21.4.8<br>21.4.9                                                 | ock Diagram of CAN Controller st of Overall Control Registers lassifying CAN Controller Registers Configuration of Control Status Register (CSR) Function of Control Status Register (CSR) Correspondence between Node Status Bit and Node Status Notes on Using Bus Operation Stop Bit (HALT = 1) Last Event Indicator Register (LEIR) Receive and Transmit Error Counters (RTEC) Bit Timing Register (BTR) Prescaler Setting by Bit Timing Register (BTR) Message Buffer Valid Register (BVALR)                                                                                                                                                                                                                                                                                                                     |            |

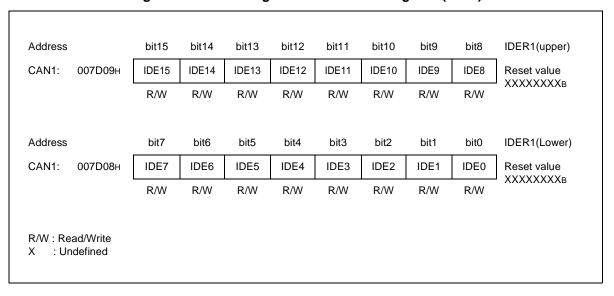

| 21.2 Bl<br>21.3 Li<br>21.4 C<br>21.4.1<br>21.4.2<br>21.4.3<br>21.4.4<br>21.4.5<br>21.4.6<br>21.4.7<br>21.4.8<br>21.4.9                                                 | ock Diagram of CAN Controller st of Overall Control Registers lassifying CAN Controller Registers Configuration of Control Status Register (CSR) Function of Control Status Register (CSR) Correspondence between Node Status Bit and Node Status Notes on Using Bus Operation Stop Bit (HALT = 1) Last Event Indicator Register (LEIR) Receive and Transmit Error Counters (RTEC) Bit Timing Register (BTR) Prescaler Setting by Bit Timing Register (BTR) Message Buffer Valid Register (BVALR) IDE Register (IDER)                                                                                                                                                                                                                                                                                                 |            |

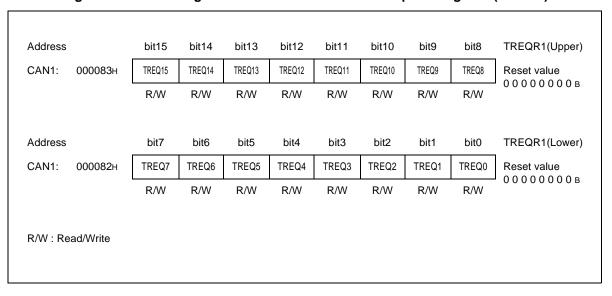

| 21.2 Bl 21.3 Li 21.4 Cl 21.4.1 21.4.2 21.4.3 21.4.4 21.4.5 21.4.6 21.4.7 21.4.8 21.4.9 21.4.10 21.4.11                                                                 | ock Diagram of CAN Controller st of Overall Control Registers lassifying CAN Controller Registers Configuration of Control Status Register (CSR) Function of Control Status Register (CSR) Correspondence between Node Status Bit and Node Status Notes on Using Bus Operation Stop Bit (HALT = 1) Last Event Indicator Register (LEIR) Receive and Transmit Error Counters (RTEC) Bit Timing Register (BTR) Prescaler Setting by Bit Timing Register (BTR) Message Buffer Valid Register (BVALR) IDE Register (IDER) Transmission Request Register (TREQR)                                                                                                                                                                                                                                                           |            |

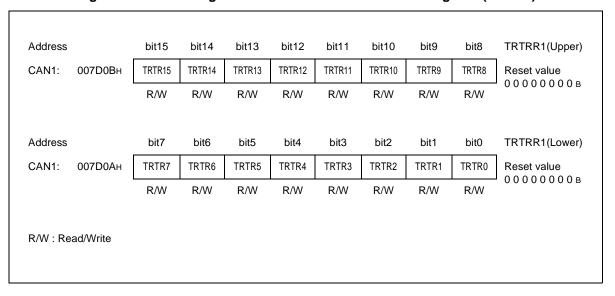

| 21.2 Bl 21.3 Li 21.4 Cl 21.4.1 21.4.2 21.4.3 21.4.4 21.4.5 21.4.6 21.4.7 21.4.8 21.4.9 21.4.10 21.4.11                                                                 | ock Diagram of CAN Controller st of Overall Control Registers lassifying CAN Controller Registers Configuration of Control Status Register (CSR) Function of Control Status Register (CSR) Correspondence between Node Status Bit and Node Status Notes on Using Bus Operation Stop Bit (HALT = 1) Last Event Indicator Register (LEIR) Receive and Transmit Error Counters (RTEC) Bit Timing Register (BTR) Prescaler Setting by Bit Timing Register (BTR) Message Buffer Valid Register (BVALR) IDE Register (IDER)                                                                                                                                                                                                                                                                                                 |            |

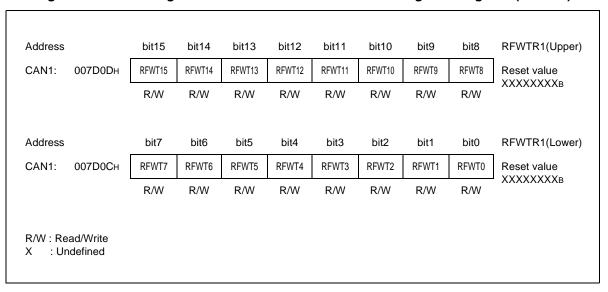

| 21.2 Bl 21.3 Li 21.4 C 21.4.1 21.4.2 21.4.3 21.4.4 21.4.5 21.4.6 21.4.7 21.4.8 21.4.9 21.4.10 21.4.11 21.4.12 21.4.13                                                  | ock Diagram of CAN Controller st of Overall Control Registers lassifying CAN Controller Registers Configuration of Control Status Register (CSR) Function of Control Status Register (CSR) Correspondence between Node Status Bit and Node Status Notes on Using Bus Operation Stop Bit (HALT = 1) Last Event Indicator Register (LEIR) Receive and Transmit Error Counters (RTEC) Bit Timing Register (BTR) Prescaler Setting by Bit Timing Register (BTR) Message Buffer Valid Register (BVALR) IDE Register (IDER) Transmission Request Register (TREQR) Transmission RTR Register (TRTRR) Remote Frame Receiving Wait Register (RFWTR)                                                                                                                                                                            |            |

| 21.2 Bl 21.3 Li 21.4 C 21.4.1 21.4.2 21.4.3 21.4.4 21.4.5 21.4.6 21.4.7 21.4.8 21.4.9 21.4.10 21.4.11 21.4.12 21.4.13 21.4.14                                          | ock Diagram of CAN Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| 21.2 Bl 21.3 Li 21.4 Cl 21.4.1 21.4.2 21.4.3 21.4.4 21.4.5 21.4.6 21.4.7 21.4.8 21.4.9 21.4.10 21.4.11 21.4.12 21.4.13 21.4.14 21.4.15                                 | ock Diagram of CAN Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| 21.2 Bl 21.3 Li 21.4 Cl 21.4.1 21.4.2 21.4.3 21.4.4 21.4.5 21.4.6 21.4.7 21.4.8 21.4.9 21.4.10 21.4.11 21.4.12 21.4.13 21.4.14 21.4.15                                 | ock Diagram of CAN Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| 21.2 Bl 21.3 Li 21.4 C 21.4.1 21.4.2 21.4.3 21.4.4 21.4.5 21.4.6 21.4.7 21.4.8 21.4.9 21.4.10 21.4.11 21.4.12 21.4.13 21.4.15 21.4.15 21.4.15                          | ock Diagram of CAN Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

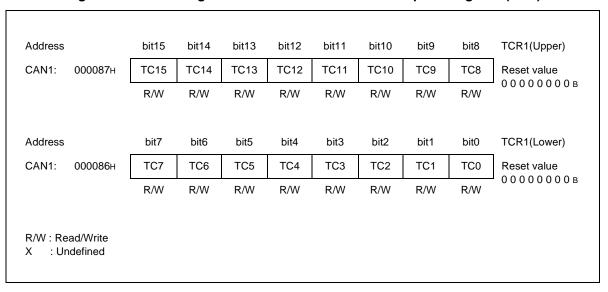

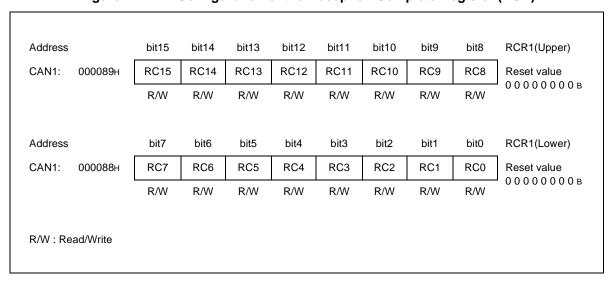

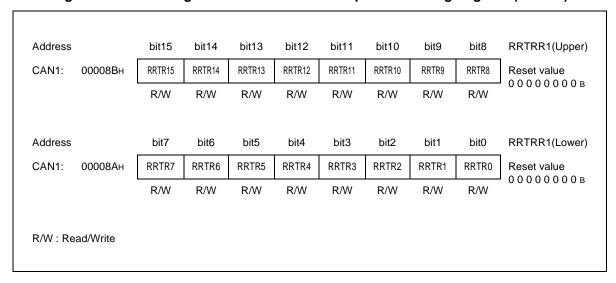

| 21.2 Bl 21.3 Li 21.4 Cl 21.4.1 21.4.2 21.4.3 21.4.4 21.4.5 21.4.6 21.4.7 21.4.8 21.4.9 21.4.10 21.4.11 21.4.12 21.4.13 21.4.14 21.4.15 21.4.15 21.4.16 21.4.17 21.4.18 | ock Diagram of CAN Controller st of Overall Control Registers  lassifying CAN Controller Registers  Configuration of Control Status Register (CSR)  Function of Control Status Register (CSR)  Correspondence between Node Status Bit and Node Status  Notes on Using Bus Operation Stop Bit (HALT = 1)  Last Event Indicator Register (LEIR)  Receive and Transmit Error Counters (RTEC)  Bit Timing Register (BTR)  Prescaler Setting by Bit Timing Register (BTR)  Message Buffer Valid Register (BVALR)  IDE Register (IDER)  Transmission Request Register (TREQR)  Transmission RTR Register (TRTRR)  Remote Frame Receiving Wait Register (RFWTR)  Transmission Complete Register (TCANR)  Transmission Complete Register (TIER)  Reception Complete Register (RCR)  Remote Request Receiving Register (RRTRR) |            |

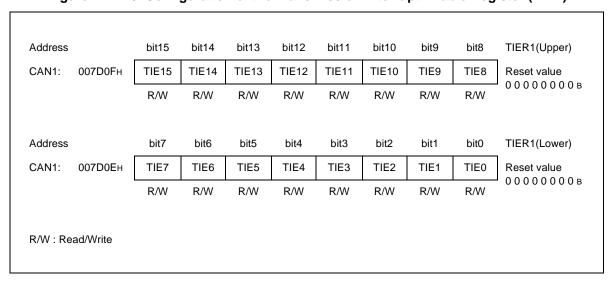

| 21.2 Bl 21.3 Li 21.4 Cl 21.4.1 21.4.2 21.4.3 21.4.4 21.4.5 21.4.6 21.4.7 21.4.8 21.4.9 21.4.10 21.4.11 21.4.12 21.4.13 21.4.14 21.4.15 21.4.15 21.4.16 21.4.17 21.4.18 | ock Diagram of CAN Controller st of Overall Control Registers  lassifying CAN Controller Registers  Configuration of Control Status Register (CSR)  Function of Control Status Register (CSR)  Correspondence between Node Status Bit and Node Status  Notes on Using Bus Operation Stop Bit (HALT = 1)  Last Event Indicator Register (LEIR)  Receive and Transmit Error Counters (RTEC)  Bit Timing Register (BTR)  Prescaler Setting by Bit Timing Register (BTR)  Message Buffer Valid Register (BVALR)  IDE Register (IDER)  Transmission Request Register (TREQR)  Transmission RTR Register (TRTRR)  Remote Frame Receiving Wait Register (RFWTR)  Transmission Complete Register (TCR)  Transmission Interrupt Enable Register (TIER)  Reception Complete Register (RCR)                                      |            |

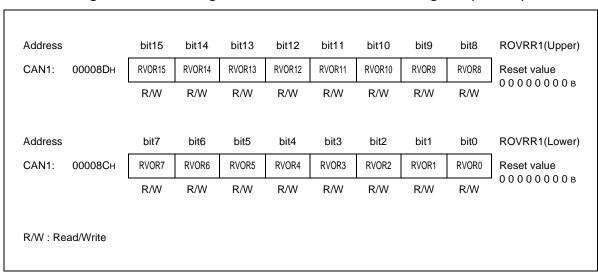

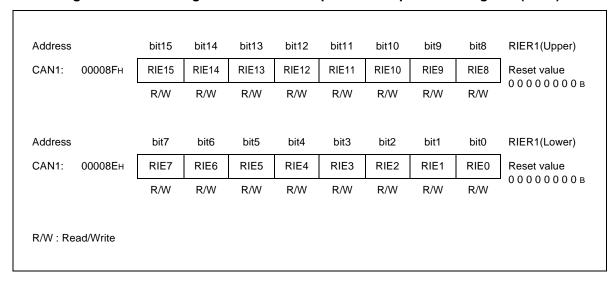

|   | 21.4.20 Reception Interrupt Enable Register (RIER)                                         | . 476        |

|---|--------------------------------------------------------------------------------------------|--------------|

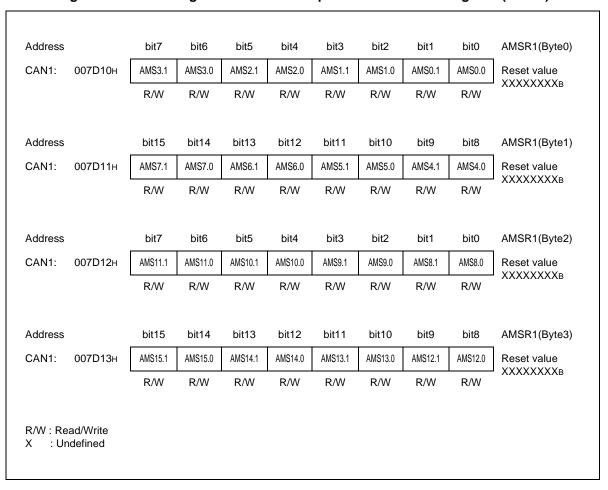

|   | 21.4.21 Acceptance Mask Select Register (AMSR)                                             |              |

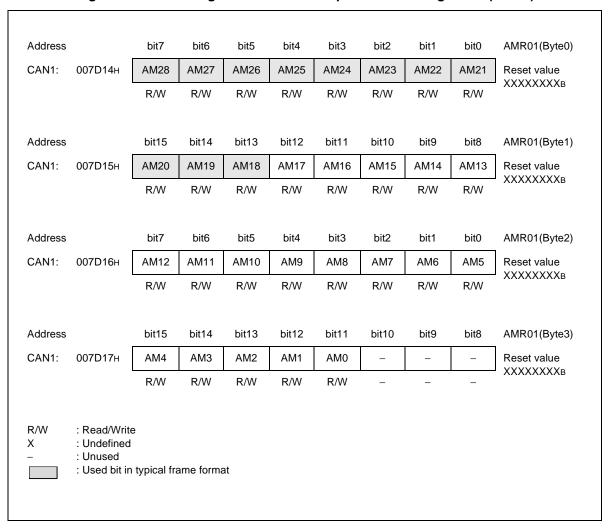

|   | 21.4.22 Acceptance Mask Registers 0 and 1 (AMR0 and AMR1)                                  |              |

|   | 21.4.23 Message Buffers                                                                    |              |

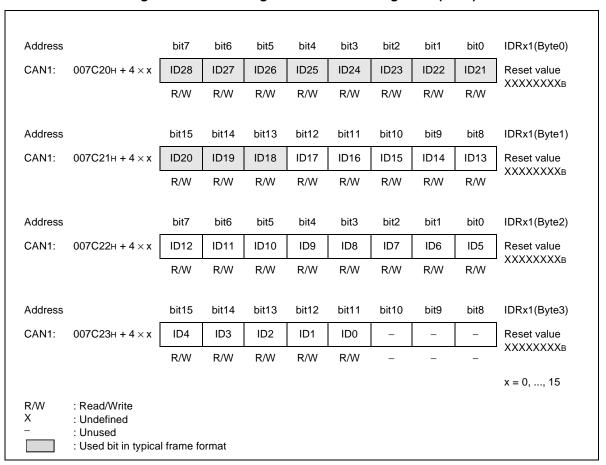

|   | 21.4.24 ID Register x (x = 0 to 15) (IDRx)                                                 |              |

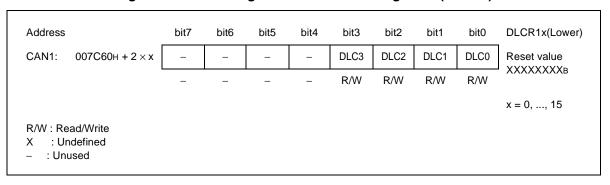

|   | 21.4.25 DLC Register x (x = 0 to 15) (DLCRx)                                               |              |

|   | 21.4.26 Data Register x (x = 0 to 15) (DTRx)                                               |              |

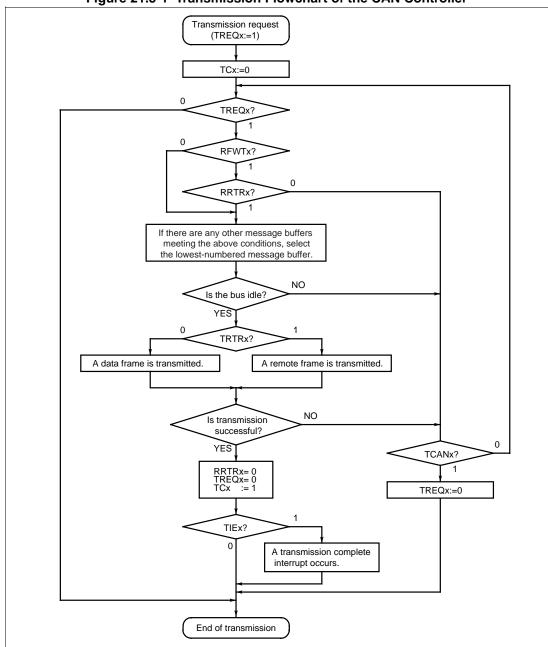

|   | 21.5 Transmission of CAN Controller                                                        |              |

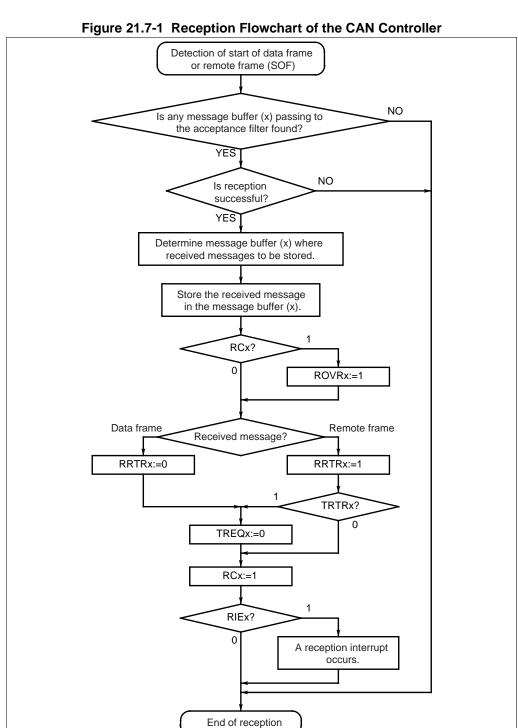

|   | 21.6 Reception of CAN Controller                                                           |              |

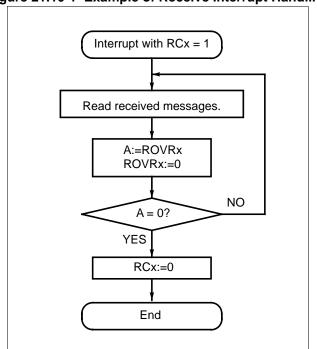

|   | 21.7 Reception Flowchart of CAN Controller                                                 |              |

|   | 21.8 How to Use CAN Controller                                                             |              |

|   | 21.9 Procedure for Transmission by Message Buffer (x)                                      |              |

|   | 21.10 Procedure for Reception by Message Buffer (x)                                        |              |

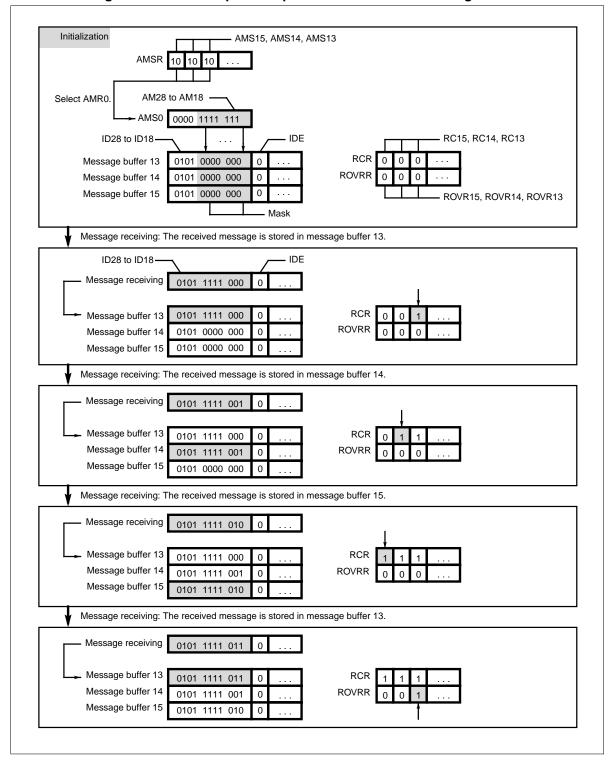

|   | 21.11 Setting Configuration of Multi-level Message Buffer                                  |              |

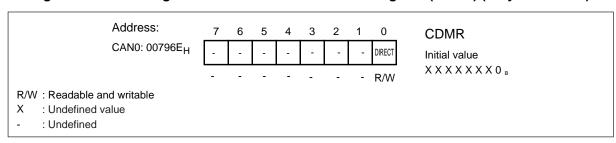

|   | 21.12 Setting the CAN Direct Mode Register                                                 |              |

|   | 21.13 Precautions when Using CAN Controller                                                |              |

|   | 21.10 1 1000000010 Whom Coming Of the Controller                                           | . 000        |

| C | HAPTER 22 ADDRESS MATCH DETECTION FUNCTION                                                 | 505          |

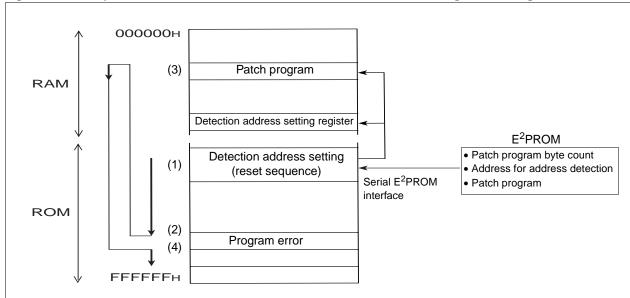

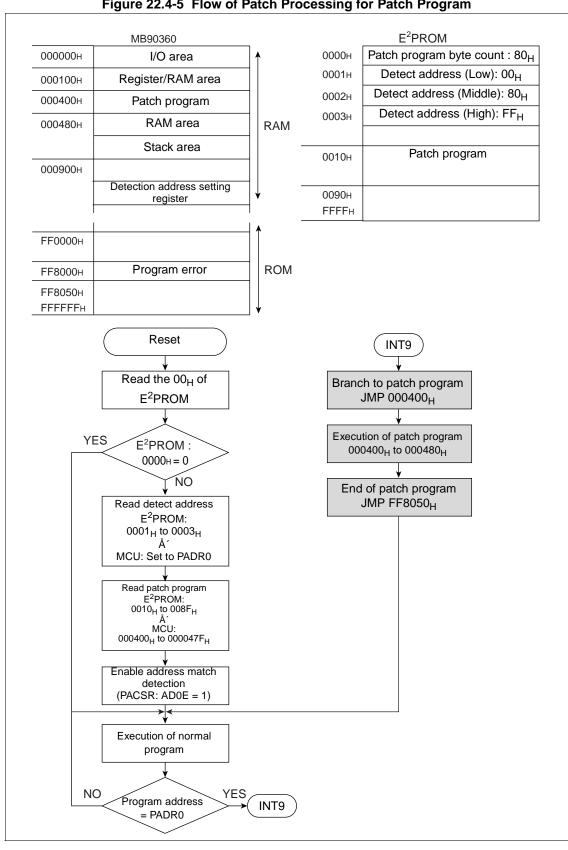

|   | 22.1 Overview of Address Match Detection Function                                          |              |

|   | 22.2 Block Diagram of Address Match Detection Function                                     |              |

|   | 22.3 Configuration of Address Match Detection Function                                     |              |

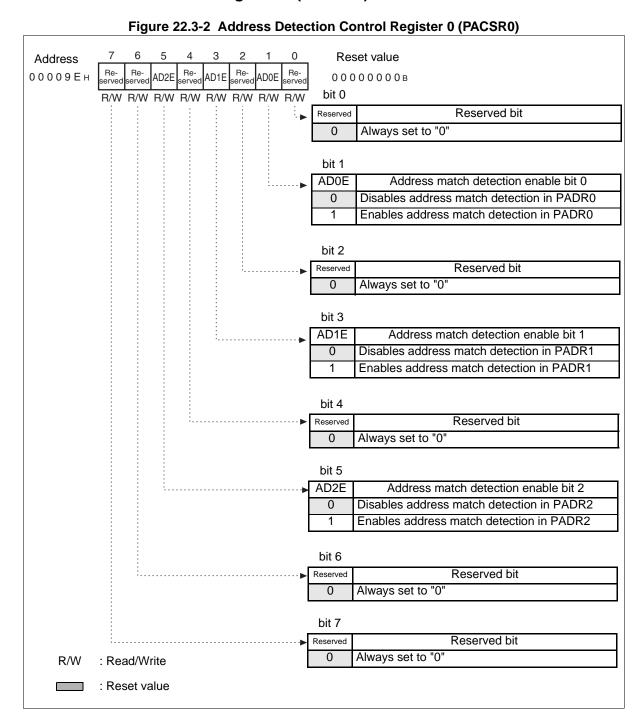

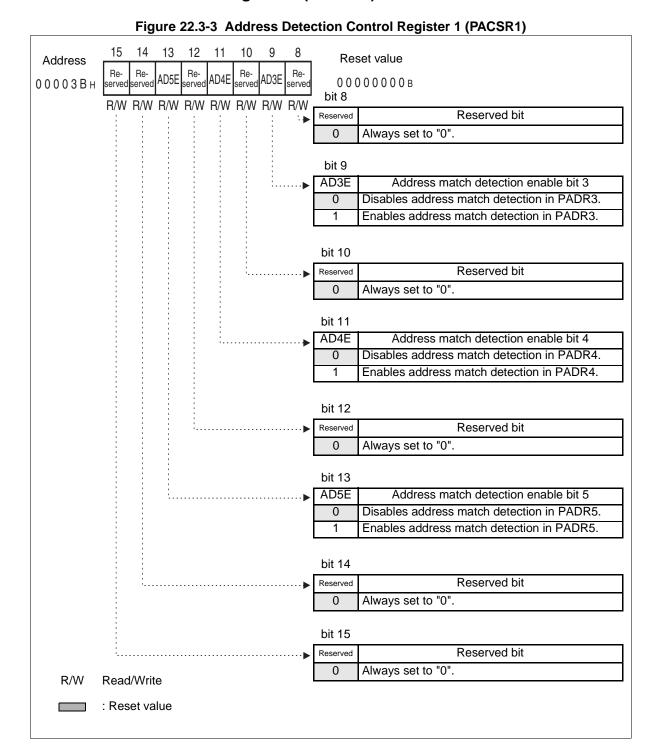

|   | 22.3.1 Address Detection Control Register (PACSR0/PACSR1)                                  |              |

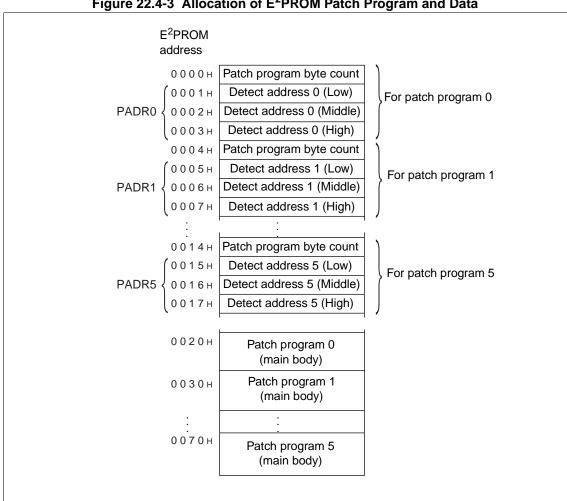

|   | 22.3.2 Detect Address Setting Registers (PADR0 to PADR5)                                   |              |

|   | 22.4 Explanation of Operation of Address Match Detection Function                          |              |

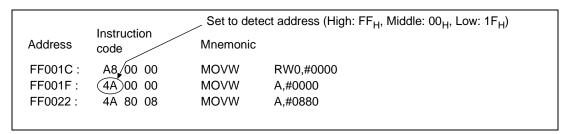

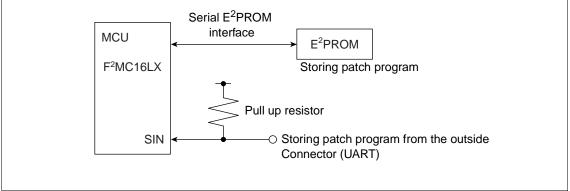

|   | 22.4.1 Example of using Address Match Detection Function                                   |              |

|   | 22.5 Program Example of Address Match Detection Function                                   |              |

|   |                                                                                            |              |